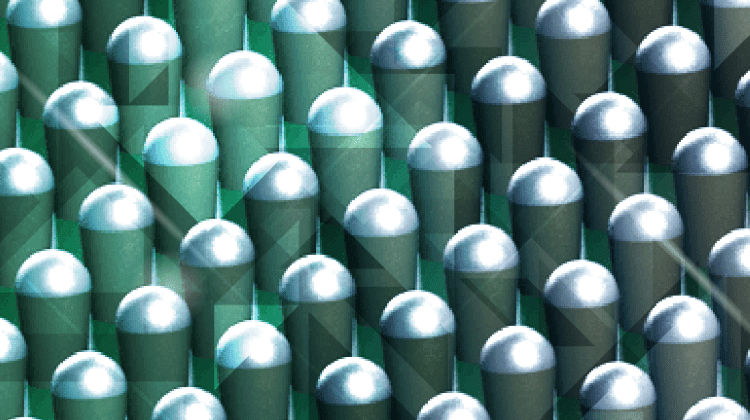

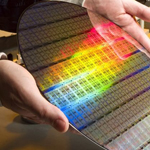

一線晶圓廠正紛紛以混搭20奈米製程的方式,加速14或16奈米鰭式電晶體(FinFET)量產腳步。包括IBM授權技術陣營中的聯電、格羅方德(GLOBALFOUNDRIES)和三星(Samsung),皆預計在2014年以14奈米FinFET前段閘極結合20奈米後段金屬導線製程的方式達成試量產目標;而台積電為提早至2015年跨入16奈米FinFET世代,初版方案亦可望採用類似的混搭技術,足見此設計方式已成為晶圓廠進入FinFET世代的共通策略。

|

| 聯華電子市場行銷處處長黃克勤提到,各家廠商在16/14奈米FinFET的技術發展齊頭並進,未來勢將引發更激烈的市場競爭。 |

聯華電子市場行銷處處長黃克勤表示,FinFET製程可有效控管電晶體閘極漏電流問題,並提高電子移動率,因而能大幅提升晶片運算效能同時降低功耗,現已成為全球晶圓廠新的角力戰場。為搶占市場先機,各家廠商也相繼祭出新的奈米製程混搭方案,期透過20奈米晶圓後段金屬導線(BEOL)製程技術,加快14或16奈米FinFET方案的量產腳步。

黃克勤進一步分析,14或16奈米FinFET對晶圓代工廠而言係重大技術革新,無論是立體電晶體結構設計、材料摻雜比例、溫度和物理特性掌握的難度均大幅攀升;尤其在BEOL方面,要在短時間內將金屬導線製程微縮至1x奈米的密度相當不容易,因此各家晶圓廠遂計畫在晶圓前段閘極製程(FEOL)先一步導入FinFET,並沿用20奈米BEOL方案,以縮短開發時程和減輕投資負擔。

其中,聯電、格羅方德和三星已先後在2012年與IBM簽訂14奈米FinFET合作計畫,並分別預定於2014年底~2015年,以14奈米FinFET FEOL混搭20奈米MEOL/BEOL的方式導入量產。

黃克勤認為,混搭方案將是推進半導體製程提早1年演進到1x奈米FinFET的關鍵布局,不僅能加速設計與測試流程,亦有助控制成本,預估晶圓代工業者初期都將採用此一架構,待技術日益成熟後才會全面升級為純16或14奈米製程。現階段,聯電已授權引進IBM在半導體材料研究方面的Know-how與技術支援,將用來優化自行研發的14和20奈米混搭製程,將於2015年正式投產。

格羅方德全球業務行銷暨設計品質執行副總裁Mike Noonen也強調,該公司將於2014年底搶先推出14nm-XM製程,可充分利用現有20奈米設備和技術資源,降低FinFET研發和製造成本,並簡化客戶新一代處理器的設計難度,盡速實現以立體電晶體結構減輕閘極漏電流的目標,進而延伸摩爾定律(Moore’s Law)至新境界。

此外,台積電近期也宣布2014年量產20奈米後,將提前1年至2015年發表16奈米FinFET製程,業界也預估其第一個量產版本將導入20奈米BEOL混搭方案,才能順利在短短1年內,從20奈米跨入16奈米世代。由此可見,一線晶圓代工業者在挺進FinFET領域的時間和成本壓力下,採用混搭結構已成為一門顯學。