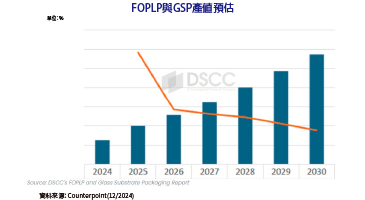

扇出封裝技術(Fan-out)在過去一年獲得市場高度關注,也成為本屆Semicon Taiwan展的焦點。扇出封裝具備超薄、高I/O腳數等優勢,是行動應用處理器非常理想的封裝技術選擇,但其成本較高也是不爭的事實。所幸終端產品追求輕薄短小與多功能整合的趨勢幾乎擴散到電子業內的每個次領域,未來系統封裝(SiP)可望成為扇出技術向下滲透的開路先鋒。

與Semicon Taiwan 2016展會同步舉行的SiP全球高峰會,今年議程以嵌入式與晶圓級封裝作為主軸,扇出封裝技術更是一大熱點。

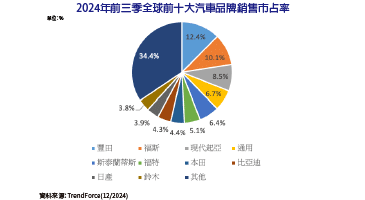

擔任峰會主席的矽品工程中心資深處長藍章益表示,目前半導體產品的應用有四大熱門領域,分別是網路通訊、智慧型手機、物聯網/穿戴式裝置與汽車電子。就晶片封裝的角度來看,除了網路通訊以及汽車動力總成(Powertrain)相關晶片有其特殊需求,在可預見的未來還會走自己的路之外,鎖定其他應用領域的晶片都跟手機晶片越來越像。

舉例來說,穿戴式裝置對產品的外觀尺寸要求,比起智慧型手機有過之而無不及;汽車資訊娛樂及先進駕駛輔助系統(ADAS)所使用的晶片元件,則對運算性能有相當高的需求,導致I/O數量跟著水漲船高。此外,目前許多車載資訊娛樂系統的元件大廠,都跟手機產業有相當淵源,例如NVIDIA、高通(Qualcomm)。這也是車用晶片越來越像手機晶片的原因之一。

整體來說,半導體產業的趨勢一直是晶片越做越小,但性能跟功能卻要不斷增加。從封裝的角度來看,這其實是有矛盾的,因為晶片面積縮小後,能夠放置I/O的面積也會跟著縮小,但更強的運算效能與多功能整合,卻會增加I/O的數量。因此,封裝技術勢必會遇到I/O密度難以進一步提升的瓶頸,而扇出技術就是解決這個問題的方法。

不過,目前最新的扇出封裝技術不只是I/O擴展而已,同時還以高分子聚合物薄膜來取代傳統IC封裝基板,使封裝厚度大幅降低。因此,精確地說,目前業界討論最熱烈的扇出封裝,應該稱為模塑化合物晶圓級晶片封裝(Mold Compound WLCSP, mWLCSP),其裸晶跟聚合物薄膜外面會有一層黑膠體來保護脆弱的內層結構。

藍章益指出,為了減少封裝厚度而改用高分子聚合物薄膜,對晶片封裝製程來說造成很大的挑戰,因為裸晶在封裝前都會經過研磨,已經相當柔軟而脆弱,高分子聚合物薄膜本身又容易翹曲變形,因此可靠度構成相當大的挑戰。不過,目前業界已經找到合適的材料與加工方法,可以確保封裝可靠度,還可以進一步在薄膜上嵌入被動元件,實現更高的整合度。

整體來說,扇出技術的進展會對整個半導體供應鏈造成相當大的影響。首當其衝的就是IC載板廠商,因為扇出技術已經不用傳統IC載板了;其次則是被動元件業者,為了滿足嵌入封裝內的需求,相關業者必須進一步把被動元件縮小到微米尺度,而且還要具備足夠的容值/阻值,這部分料將牽涉到被動元件材料的研發及突破。

由於導入大量新技術跟新材料,扇出封裝雖然有更輕薄短小、可支援更高I/O數量等優勢,但成本也會跟著墊高。因此,高階、高單價,需要大量I/O的晶片,較有機會優先採用扇出封裝,例如應用處理器。

然而,對專業封裝廠來說,這種機會大多會被晶圓代工廠捷足先登,因此相關業者必須要找出其他具有發展潛力的應用,才能開拓自家的扇出封裝業務。而其中最有潛力的就是SiP應用。

藍章益分析,SiP是高度客製化的封裝產品,利潤空間較高,因此對封裝廠來說,針對SiP客戶推廣扇出封裝業務,投資回收的速度會比較快。另一方面,SiP封裝採用扇出技術,能夠為客戶帶來的效益也更明顯,例如封裝厚度大幅縮減。

因此,SiP對專業封測廠來說,是發展扇出封裝業務項目的主要機會所在。這類產品的單價雖不如高階處理器,但仍有數美元水準,而且客戶也比較容易看到扇出技術所能帶來的效益,接受度較高。目前矽品已經有扇出SiP專案正在進行中,預計2017年將能開花結果。