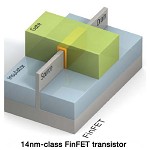

賽靈思(Xilinx)將搶先在競爭對手Altera之前,發表16奈米鰭式場效電晶體(FinFET)現場可編程閘陣列(FPGA)。面對Altera採用英特爾(Intel)14奈米三閘極電晶體(Tri-gate Transistor)製程,並將於2016年量產14奈米FPGA的攻勢,賽靈思於日前發動反擊,將攜手台積電採用16奈米FinFET製程,搶先於2014年推出新一代FPGA。

賽靈思總裁暨執行長Moshe Gavrielov表示,16奈米先進製程中的三維(3D)電晶體將能夠讓客戶擁有更高效能、更低耗電的產品。賽靈思與台積電於16奈米製程的合作將延續雙方過去在各項先進製程上所獲得的成果。

值得一提的是,因著與賽靈思的合作,台積電也宣布將16奈米FinFET製程技術的生產時程提前,將於今年發布16奈米FinFET製程測試晶片,而首批FPGA產品將於2014年問世。反觀英特爾則預計在2014年將第二代三閘極電晶體技術導入14奈米製程,並用以量產新中央處理器(CPU)。

據了解,賽靈思與台積電將共同推動一項名為FinFast的專案計畫,以台積電16奈米FinFET製程技術打造高速、低耗電、高效能的FPGA元件;雙方投入所需資源組成專屬研發團隊,針對FinFET製程與賽靈思UltraScale架構共同進行最佳化。UltraScale為賽靈思全新的特定應用積體電路(ASIC)等級架構,能針對從20奈米平面式製程到16奈米以及更先進的FinFET製程進行微縮,亦可透過3D積體電路(IC)技術進行系統單晶片(SoC)的微縮。

Gavrielov指出,相較於前幾個世代的製程,16奈米製程的技術複雜度高出許多,且將耗費賽靈思更多的研發成本。賽靈思在28奈米製程的研發投資為8億美元,而先進製程的研發投資金額則至少為80億美元。儘管如此,由於擁有先進製程技術的晶圓代工廠數量正不斷增加,因此,在市場變化的帶動下,投資數字大幅度躍進的情形將會有稍許的改善。此外,賽靈思為確保每個製程能具備成本效益,將花5年以上的時間設計產品,並將每項產品的生命週期延長到至少15年。

與此同時,賽靈思也將使用台積電的半導體整合生產技術–CoWoS(Chip on Wafer on Substrate),實現高階3D IC系統整合及系統級效能。