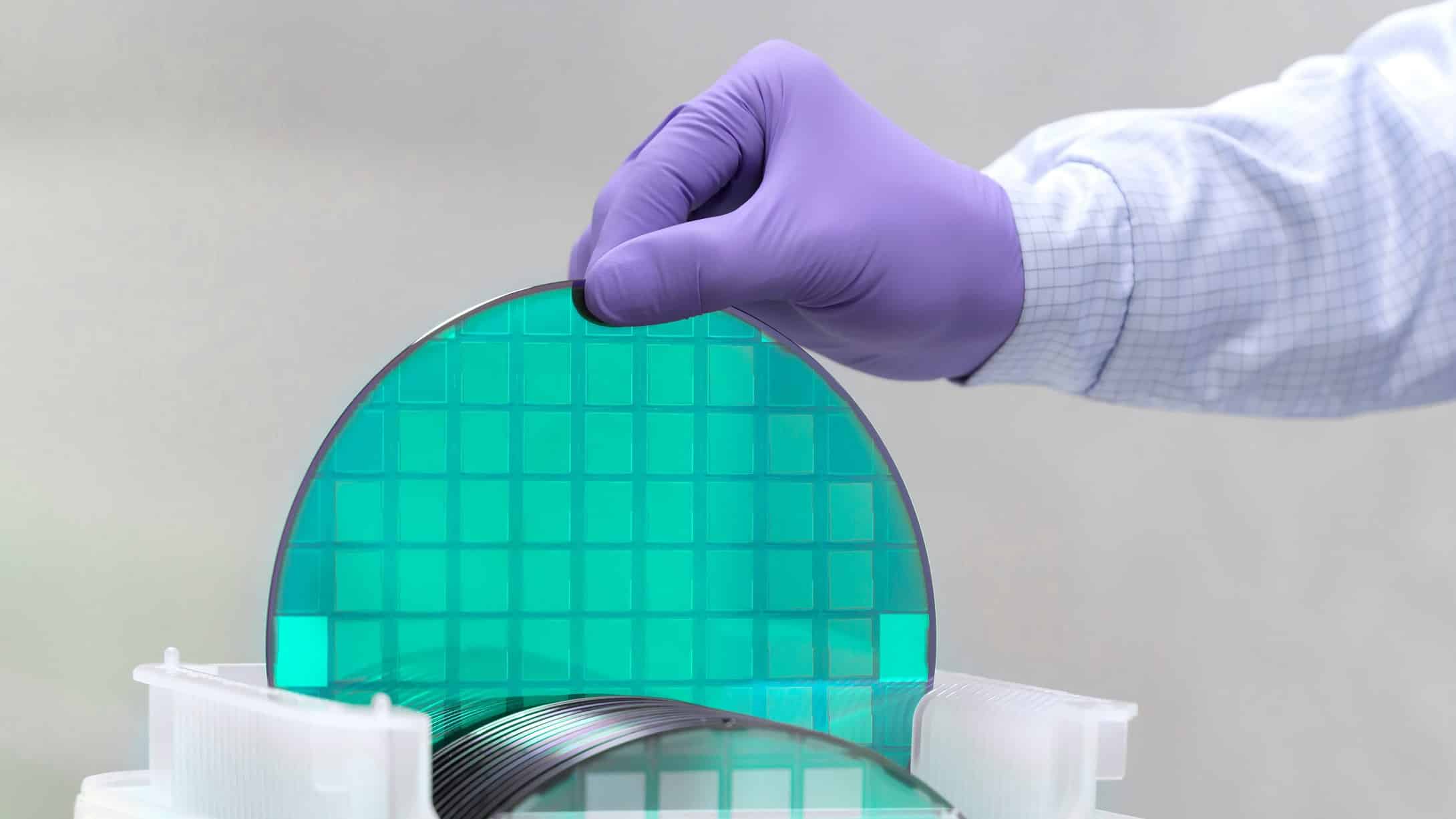

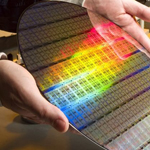

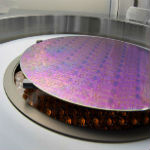

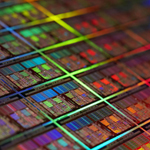

聯電14奈米(nm)鰭式電晶體(FinFET)製程技術將於後年初開始試產。聯電正全力研發新一代14奈米FinFET製程技術,預計效能可較現今28奈米製程提升35~40%,可提供通訊晶片與應用處理器低功耗與高效能優勢,擴大搶攻通訊與消費性電子IC製造商機。

|

| 聯電執行長孫世偉表示,14奈米FinFET製程技術將會是聯電切入未來次世代通訊運算市場的最佳利器。 |

聯電執行長孫世偉表示,由於晶圓從28跨入20奈米製程以下的微縮過程中,勢必得使用雙重曝光(Double Patterning)微影技術才能實現,而此一技術無論是微影機台或人力研發等成本都相當高昂,因此造成許多出貨量不大的IC設計商不願投資大筆資金導入,間接使20奈米市場需求無法擴大。

具備低功耗特性的FinFET製程技術,儘管仍無法省去雙重曝光微影技術的成本,但卻能大幅提升單位面積內電晶體的整體效能,降低IC設計商因雙重曝光微影技術所帶來的成本衝擊,因此遂成為各家晶圓代工業者爭相競逐的技術。

孫世偉進一步指出,在IBM FinFET技術授權的基礎下,聯電將跳過20奈米製程,直接跨入14奈米FinFET製程技術,藉此為通訊與行動運算領域客戶提供更具效能優勢的解決方案。此一新製程目前正於南科研究中心全力研發中,預計2014年初可完成驗證,並旋即進行試產。

然而,相較於台積電與格羅方德(GLOBALFOUNDRIES)均表示將於2014年初量產16/14奈米FinFET,聯電量產時程顯然稍慢,如何後發先至遂成為業界關注焦點。孫世偉強調,儘管聯電在此一製程上的研發起步較晚,但相對FinFET製程所需的機台製造技術亦較為成熟,且設備價格也較為便宜,再加上與IBM技術交流等助益,未來量產品質與時程都將可較競爭對手更符合客戶需求。

另一方面,聯電28奈米產品線則可望於年底量產,並於明年第一季開始貢獻營收。孫世偉補充,首波28奈米Porting產品在經過幾個月元件及製程參數調整後,良率已獲得顯著提升,且公司亦於第三季成功投片(Tapeout)使用28奈米後閘極(Gate-last)高介電質金屬閘極(HKMG)製程的行動通訊產品,並陸續與相關客戶密切合作中。

據悉,目前聯電晶圓廠產能利用率為84%,其中,40奈米先進製程比重持續提升中,且平均銷售單價較上季攀升,並已刺激營業收入向上成長,而營收貢獻亦從第二季9%成長至第三季的13%,年底前則可望到達15%。

除標準產品外,聯電也開始提供適用於觸控晶片領域的解決方案–embedded Flash特殊製程技術平台,並已有數家主流觸控廠商開始採用,而這些特殊製程技術也可望為聯電營收成長注入全新動能。

此外,對於各大晶圓廠皆預期第四季與明年初營收成長將趨緩,孫世偉表示,現今晶圓代工製造正處在庫存調整及景氣循環週期中,聯電預估此波庫存調整將持續至明年初,景氣回溫的脈動將取決於明年總體經濟、終端產品市場需求與新產品交替力道強弱;而公司未來將持續擴大客戶層面,改善產品組合,並進一步提升產能調配的彈性來降低週期性波動所帶來的衝擊。