功率半導體的並聯分成幾個層級, 最常見的是功率模組內部的晶片層級,這些層級可以達到更高的額定電流。其根據是,晶片只能設計為限定的額定電流,因此需要並聯多個晶片才能達到所需的額定電流。並聯可發生在單獨的模組層級,例如將六開關模組的三個支路並聯,便能建立一個額定電流為單獨支路三倍的半橋模組。另外,也可以採使用多個獨立封裝(例如TO-247)或一起切換的模組的形式,這裡將聚焦在後者的並聯範例。

任何嘗試過的人都知道,硬並聯絕緣閘極雙極性電晶體(IGBT)功率模組是一個多面向的技術挑戰,需要擁有功率配置、閘極驅動器設計、熱平衡、統計分析、磁場效應上的經驗,甚至還要一些直覺。因此,聰明的工程師在著手並聯碳化矽(SiC) 功率半導體的任務時,應該要抱持一絲謹慎的心態,因為更快的開關速度代表著時序和電感將非常關鍵。本文希望說明主要的技術障礙,並分享一些並聯多重SiC金屬氧化半導體場效電晶體(MOSFET)模組的實務經驗。

並聯SiC模組

與此主題相關的最根本問題是:為何要使用並聯模組?並聯兩個200安培(A) 模組來製造一個400安培的模組,可得到哪些好處?那何不直接使用一個400 安培的零件?從商業領域來看,1,200伏特(V)等級的IGBT模組提供了高達3,600安培的多種額定電流和封裝。但對SiC MOSFET來說,更高電流(>400安培)的選項受到更多限制,尤其是需要使用產業標準的封裝或多重來源時。此外,相比於體積較大但產量較低的封裝,體積更小的封裝通常可以用較低的成本大量生產。

但是,會並聯模組主要是為了技術性原因,這些原因在SiC MOSFET上來說比IGBT更重要,原因包含,一是多個封裝可以分散在散熱器上並改善散熱效果,如此可以從更昂貴的SiC MOSFET模組傳送更多電流。其次,較大的實體封裝由於實體間距及使用螺絲端子連接來承載較高的電流,在電源迴路和閘極驅動器電路中均具有較高的電感。三是使用大量晶片會使所有晶片的內部對稱配置和閘極電感均衡變得極為關鍵,且很難對具有有限端子選項的封裝進行最佳化。最後,前兩點可達到更快的開關速度,因此使用這些較小的封裝可實現更低的開關損耗以及在關斷期間更低的電壓過衝。

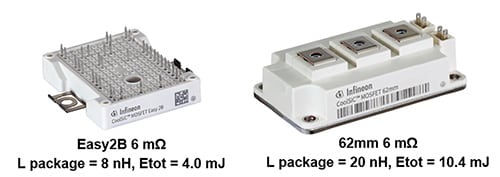

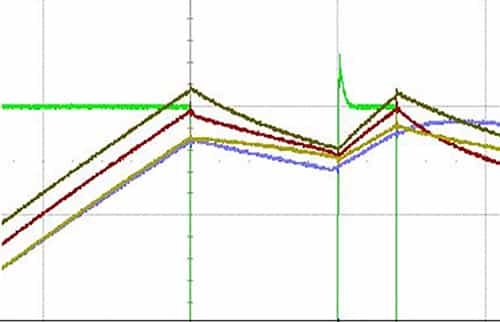

透過比較在採用兩個產業標準模組(一個為PCB型,另一個62毫歐姆模組)封裝中的相同6毫歐姆(mΩ)晶片組,便能說明其中的一些論點,如圖1所示。可以看出,相比於PCB型的薄型封裝,62毫米(mm)模組的迴路電感為兩倍以上,開關損耗也是兩倍以上。

IGBT/SiC MOSFET並聯差異

透過進一步檢驗,儘管並聯SiC MOSFET的開關速度較快,但與IGBT相比仍具有一些優勢。

與Si IGBT VCE sat特性相比,SiC MOSFET通常有較高的RDS(on)正溫度係數,這可作為靜態電流共用期間的負反饋。如果一台裝置消耗的電流更大,這些晶片或模組將變熱而增加RDS(on),進而降低電流。因此,此負反饋將降低熱不平衡的程度。

Si IGBT的開關損耗會隨溫度升高而大大增加,這對溫度不平衡具有正反饋作用。較熱的晶片具有較高的損耗,因此將變得更熱。SiC MOSFET的開關損耗隨溫度增加的幅度非常小,大大降低了此效應。

此外,SiC MOSFET具有軟跨導曲線,代表當其在閘極臨界值區域運作時,閘極電壓的細微變化對汲極電流的影響要小於同級的Si IGBT。如此對動態電流共用有所幫助。

關於英飛凌溝槽閘極裝置的統計分析指出,從參數分布來看,具有較高RDS(on)的模組具有較低的開關損耗,有助於匹配零件之間的損耗。

體驗並聯測試平台

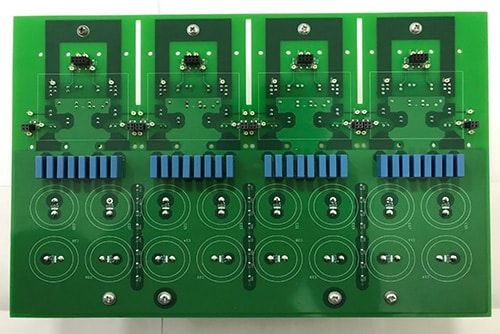

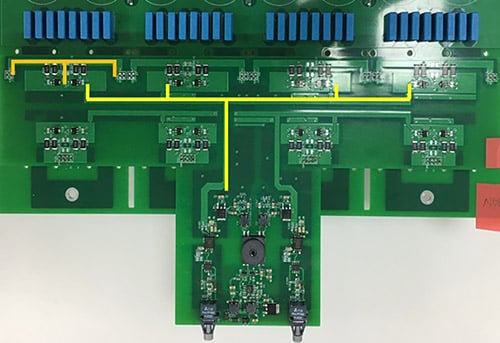

圖2顯示一個測試平台,該平台設計用於評估並聯運作的多個SiC MOSFET模組的效能。圖中是一個功率PCB,內含四個並聯的6毫歐姆1,200伏特SiC MOSFET半橋模組。這裡將考量此設計平台的幾個方面。

模組內部配置

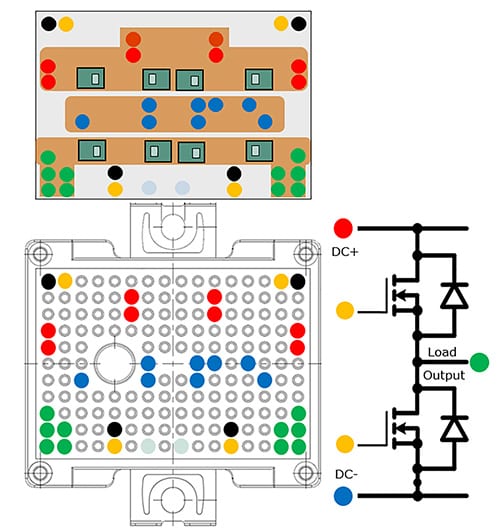

並聯首先必須考慮模組內部的功率和閘極配置。以圖3的模組為例,其顯示如何設計內部晶片配置和模組接腳,為並聯的多個晶片提供相同且對稱的功率和閘極驅動器配置。同時,還能維持在較低的電感配置開關迴路電感。

一般來說,PCB型模組樣式的接腳閘陣列讓配置提升彈性以獲得最佳化。

功率PCB配置

從功率配置來看,如圖3所示,此模組分為兩個對半。為符合此對稱性,圖4顯示的功率配置由中心線下方的鏡像構成,就像蝴蝶的翅膀一樣。這能讓模組內部晶片之間保持對等的電流共用。四個模組中的每個模組均使用完全一模一樣的配置,以使模組之間的電流共用相等,請見圖2。保持低外部開關迴路電感也很重要,這可以透過將DC+和DC-匯流排連接與多個PCB銅平面重疊,以及使用局部解耦電容器來達成。

閘極驅動器電路設計

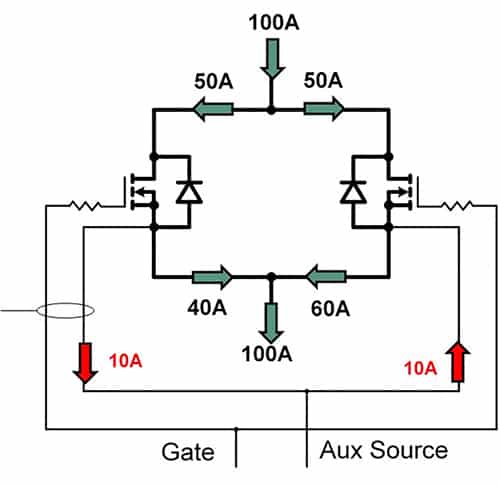

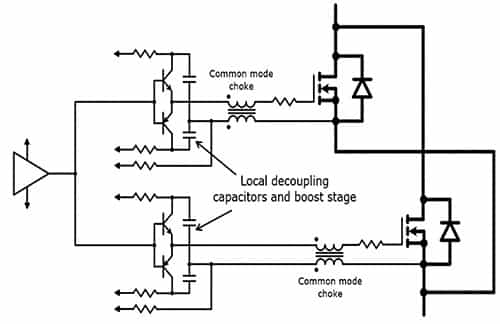

當對有多個閘極連接的所有四個模組使用共用的閘極驅動器電路時,重要的是減少在輔助源極連接中流動的任何電流。圖5顯示,在兩個模組的簡化範例中,輔助源極連接如何提供連往主電流路徑的自然並聯傳導路徑。有些電子可以在此輔助源極並聯路徑中流動,它們喜歡走不同於其他人的路徑,因此稱其為「青少年電子」。此電流可能大到足以引起閘極振盪,甚至熔斷模組內部的輔助黏合線。

圖6中的電路用於減少這些非必要的循環電流。這是共模扼流圈的組合,在流入和流出電流相等的標準閘極電流中顯示出低阻抗,但對只在源極連接中流動的非必要源極電流卻顯示出高阻抗。除此之外,每對裝置閘極連接均使用獨立的局部升壓級。這會在源極連接中產生電阻,但使用局部電容器時,在此路徑中流動的任何電流都不會影響閘極波形。但如果只使用一個簡單的源極電阻器,則情況將不同,因為流入該源極電阻器的任何電流都會影響閘極源極電壓,進而降低直接控制的電位並提高閘極振盪的可能性。

閘極驅動器PCB配置

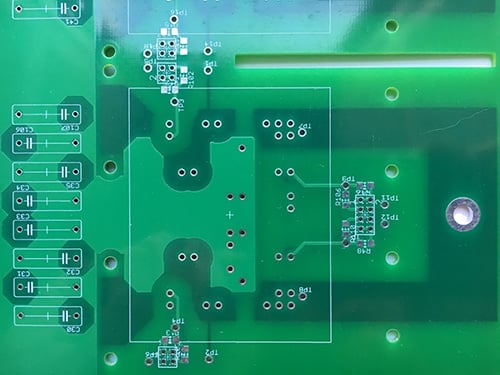

如圖3所示,6毫歐姆模組具有雙閘極源極接腳及雙電源汲極和源極連接點,用於降低電感及改善模組內部SiC MOSFET晶片之間的功率共用。閘極配置的首要挑戰,便是使兩對的閘極源極連接都具有對稱的配置。此對稱性是透過將夾層閘極驅動器PCB安裝在功率PCB上來實現(圖7)。

之後,關鍵是同時打開和關閉所有四個模組的閘極。圖8中以黃色反白顯示的「樹狀」結構透過具有相似長度的低電感線組來實現此作法。如圖8左上角橘色所示,每對閘極電路連接的局部升壓級配置都是對稱的。測量顯示較差的情況, 切換期間閘極的時脈偏移差異小於5奈秒(ns)。

使用測量儀器

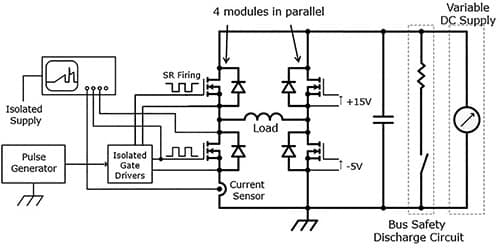

圖9顯示用於雙脈衝測試(DPT)的示意圖。務必使用設定為半橋的拓撲來測量電流共用,這樣電流和磁場才能與最終應用相匹配。此外,還必須有能力為測試的互補裝置產生同步整流器開關脈衝, 其死區時間要能滿足系統的死區時間要求。

為測量汲極和源極電流,DC匯流排PCB線路的兩側都帶有孔,因此可以使用Rogowski線圈。這些範例顯示在圖10中,其能測量DC-匯流排中的電流(即低側開關的源級電流)和DC+匯流排電流(即高側裝置的汲極電流)。此外,須保留公差,使其能測量兩組模組輸出接腳之間的輸出電流平衡。圖11顯示測量DC-匯流排電流的Rogowski線圈。

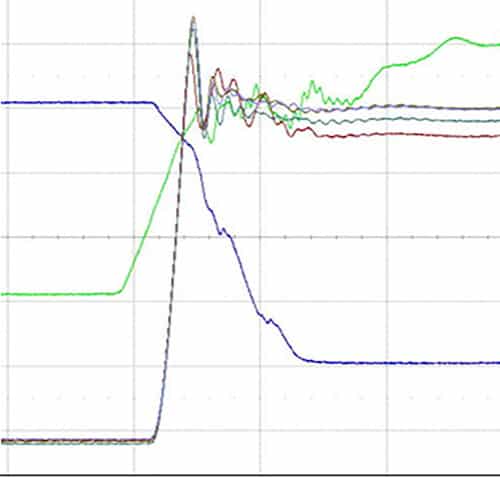

靜態電流共用

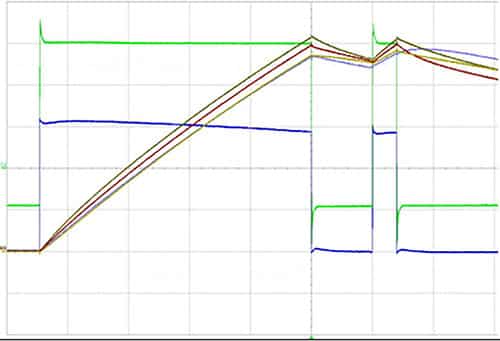

圖12顯示DPT期間四個低側裝置的源極電流。在死區時間之後,在第一個脈衝之後使用同步整流開啟高側SiC MOSFET;但不是在第二個脈衝之後,其不會使電流續流通過高側本體二極體。四個匹配模組的電流共用為+/-3%。請注意,當MOSFET未閘極且僅本體二極體導通電流時,電流共用在第二個脈衝之後將變得更糟。

最初的測試是選用RDS(on)變化小於2%的模組進行,也使用RDS(on)變化為7%的模組進行測試,共用的邊際惡化率僅+/- 4%。在高溫和開關高側裝置的其他測試中也顯示出同樣出色的效能。圖13顯示圖12中電流波形的放大圖。

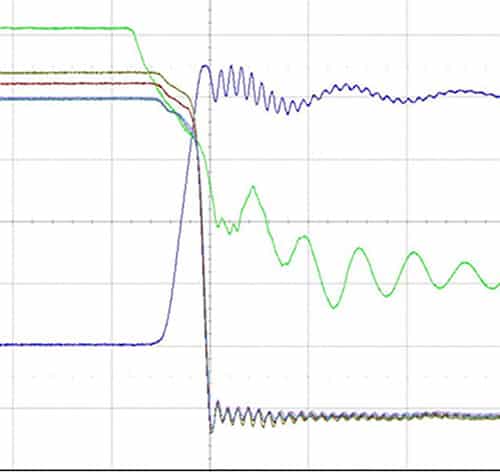

動態電流共用

如圖14和圖15所示,低側裝置的導通和關斷波形的動態共用表現出優異的共用特性。未發現電流振盪,這表示裝置在導通和關斷時脈期間共用電流。在不同的溫度下測試,在RDS(on)變化為7%下對高側裝置進行測量,均展現出相似的效能。

實驗室和量產環境下的電流共用

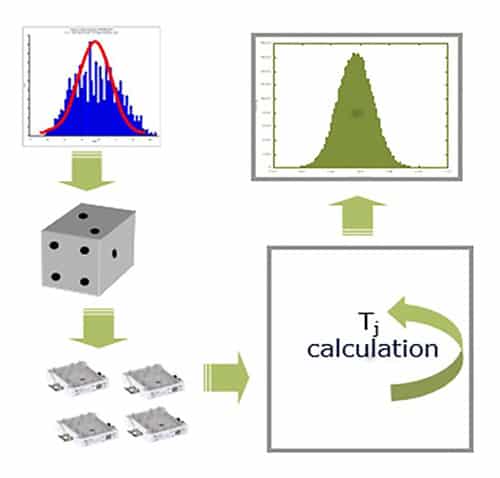

在實驗室中,透過使用少量樣本,顯示出優異的電流共用。但是,如果要將此設計轉換為量產的商業化產品,則必須計算隨機選擇的模組及其電子參數常態分布的電流共用。

此計算方法稱為蒙地卡羅分析法(Monte Carlo analysis),以蒙地卡羅著名的賭場命名。此分析的方塊圖如圖16所示。從RDS(on)的統計生產範圍和開關損耗值中選擇一組四個模組(隨機選擇每一個)。使用每個模組的這些參數,可以計算出每個模組中的電流並預估接面溫度。由於RDS(on)和開關損耗受溫度影響,因此使用迭代來計算每個模組的最終電流和接面溫度。將此流程重複套用到例如50,000 個隨機選擇的模組組合,然後計算Tj的常態分布。在此情況下,結果的變異為+/- 7C +/-三個標準差。計算中的另一個難題是,RDS(on)與開關損耗Etot之間存在互相關聯,RDS(on)較低的零件趨向產生較高的Etot值。

總結來說,四個模組可以在靜態和動態作業條件下並聯且展現出色的電流共用, 而且透過蒙地卡羅分析法隨機選擇零件, 即使量產產品仍能達到良好的共用特性。在並聯功率半導體時,必須特別留意閘極驅動器的輔助循環電流,此外工程師當然也必須遵循三個最重要的設計規則,第一個是對稱性,其次是對稱性,第三個還是對稱性。

(本文作者任職於英飛凌)