負責主導DRAM產業標準制定工作的JEDEC,近日再度針對DDR5記憶體發表新標準JESD79-5A。據JEDEC表示,在這次發布的新標準中,添加了多項可提高DDR5記憶體可靠度與效能的新功能。高效能運算、個人電腦等會使用到DDR5記憶體的應用,都可望從這個標準中獲益。

JEDEC表示,自DDR5標準發布後,業界提出許多希望進一步提高DDR5記憶體可靠度的呼聲,例如把Bounded Falt Error-correction、Soft Post-Package Repair(sPPR)、 Memory Built-In Self-Test Post Package Repair(MBIST與mPPR)、Adaptive RFM等機制納入標準中,同時也希望DDR5能支援MR4 extension。因此,這些機制都被納入到最新的DDR5標準中。

此外,JESD79-5A也進一步擴展了DDR5的時序定義跟傳輸速度,其核心速度擴展到6400MT/s、IO的AC時序速度則提高到5600MT/s,以便讓整個生態系統能推出支援5600MT/s的DDR5記憶體。這次標準更新也把核心時序參數的命名法則跟定義重新整理,以便銜接即將推出的JEDEC JESD400-5 DDR5 SPD Contents第一版標準。

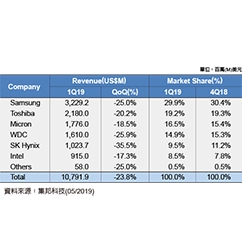

JEDEC主席Mian Quddus表示,DDR5標準的快速改版更新,象徵著JEDEC持續改進DDR5的決心,也是整個產業為客戶提供更好方案的共同努力成果。包含超微(AMD)、英特爾(Intel)、美光(Micron)、三星(Samsung)、SK海力士(SK Hynix)等CPU大廠及DRAM供應商,都將支持最新改版的DDR5標準。