益華電腦(Cadence)將持續擴大於半導體先進製程的投資規模。益華電腦為持續鞏固於先進製程市場的地位,除將與台積電保持密切合作外,更將加強矽智財(IP)陣容、設計工具以及印刷電路板(PCB)設計技術優勢,並轉型成為系統設計實現(System Design Enablement)廠商,建立獨特競爭優勢。

益華電腦總裁暨執行長陳立武表示,包括台積電、三星(Samsung)及格羅方德(GLOBALFOUNDRIES)皆十分看好鰭式電晶體(FinFET)技術未來的發展,皆將於16/14奈米(nm)製程中採用,因此益華電腦將全力投資FinFET及三維(3D)積體電路(IC)的設計技術,其中包括IP、設計工具及PCB設計三大方向。

陳立武進一步指出,該公司去年大規模併購多家IP廠商,包括Cosmic Circuits、Tensilica、Evatronix的IP事業,以及傳威(TranSwitch)的高速介面IP資產,拓展IP產品陣容,因而在Gartner的IP市場排名報告中,從2012年的十名之外迅速躍升至第四名的地位。

陳立武強調,該公司的IP聚焦於記憶體、高速傳輸介面、音訊及影像應用,大致上可分兩個種類,其一是驗證(Verification)IP,其二則是設計(Design)IP,後者已獲得超過十家以上客戶青睞,且將於FinFET製程中採用,因此未來持續提升IP陣容將是重要經營方向。

此外,針對FinFET製程元件的設計需求,益華電腦將著重於創新設計平台的開發,例如Tempus時序(Timing)Signoff解決方案及Voltus IC電源完整性(Power Integrity)解決方案等,前者可大量平行分散處理,供Signoff靜態時序分析,後者的效能則比現有方案快十倍。

事實上,益華電腦已於日前宣布其數位與客製(Custom)/類比(Analog)工具通過台積電16奈米FinFET製程的V1.0設計參考手冊(DRM)與SPICE認證,因此雙方客戶可以利用益華電腦的設計工具,將以FinFET製程為基礎的設計投入試產。

值得關注的是,益華電腦未來將由傳統電子設計自動化(EDA)工具供應商的角色,轉變成為系統設計實現公司,因此該公司除聚焦系統單晶片(SoC)的開發外,也開始注重封裝、電路板、軟體與系統層IP等系統元件的設計、整合、分析及驗證。

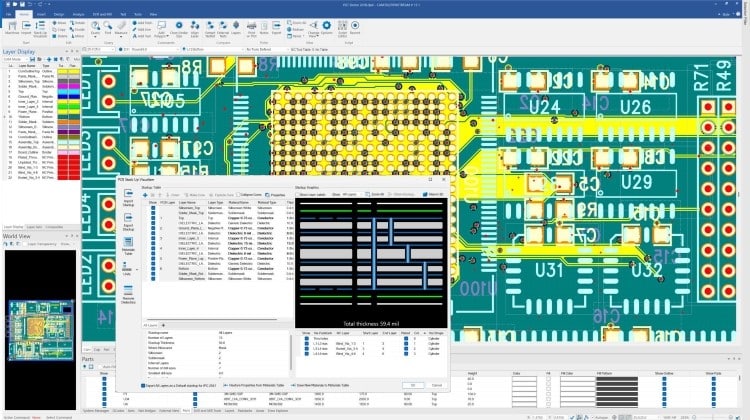

舉例而言,益華電腦於2012年併購Sigrity後,將訊號完整性分析功能整合至Allegro PCB產品系列中,而現在針對電路板的設計需求,該公司可以透過Allegro套裝、電路板設計產品以及Sigrity分析工具,提供整合式設計、分析與Signoff解決方案。

陳立武強調,16奈米製程中有高達八成的SoC開發成本係來自於軟體、驗證與確認,而益華電腦未來將推動混合式(Hybrid)的驗證方法,結合虛擬平台模型與模擬(Emulation)功能。例如展訊及聯發科皆已採用該公司的Palladium XP模擬平台,實現SoC驗證與系統級驗證,其中尚包括韌體(Firmware)及作業系統(OS)等軟體驗證項目,藉此可縮短至少6個月的上市前置時間。