新思科技(Synopsys)近日宣布其數位與客製化/類比設計流程已通過台積公司N2製程技術認證,將加速更高品質的先進製程節點系統單晶片(SoC)交付時程。

上述兩種流程具有強勁的市場動能,其中數位設計流程已達成多次實際投片,而類比設計流程也獲得數個設計專案的採用。在Synopsys.ai全端AI驅動EDA套件的支援下,相關設計流程不但讓生產力大幅提升,同時可在台積公司的各個製程節點上加速設計的遷移。

新思科技為台積公司N2製程開發的基礎IP與介面IP,將協助降低整合風險,並加速高效能運算(HPC)、AI與行動SoC上市時程。此外,新思科技旗下由AI驅動的設計技術,包括DSO.ai在內,讓台積公司得以加快N2設計的優化,以提高功耗、效能與面積(PPA)。

台積公司設計建構管理處負責人Dan Kochpatcharin表示,為先進SoC設計提供高水準的結果品質與更快的上市時程,是台積公司與新思科技長期合作的指標。台積公司與包括新思科技在内的設計生態系統合作夥伴密切合作,為客戶提供基於台積公司最先進製程技術的全方位的一流設計方案,為共同的客戶提供明顯的優勢,滿足高性能應用晶片的需求;同時藉由已通過驗證的方法可將設計從一個節點快速遷移到另一個節點。

新思科技EDA事業群策略與產品管理副總裁Sanjay Bali表示,針對台積公司N2製程節點開發的新思科技數位與類比設計流程,代表新思科技對整個EDA技術全面性的重大投資,可以協助設計人員加速2奈米晶片設計;利用越來越優化的功耗、效能與晶片密度與其他SoC有所區隔,並加速產品上市時程。

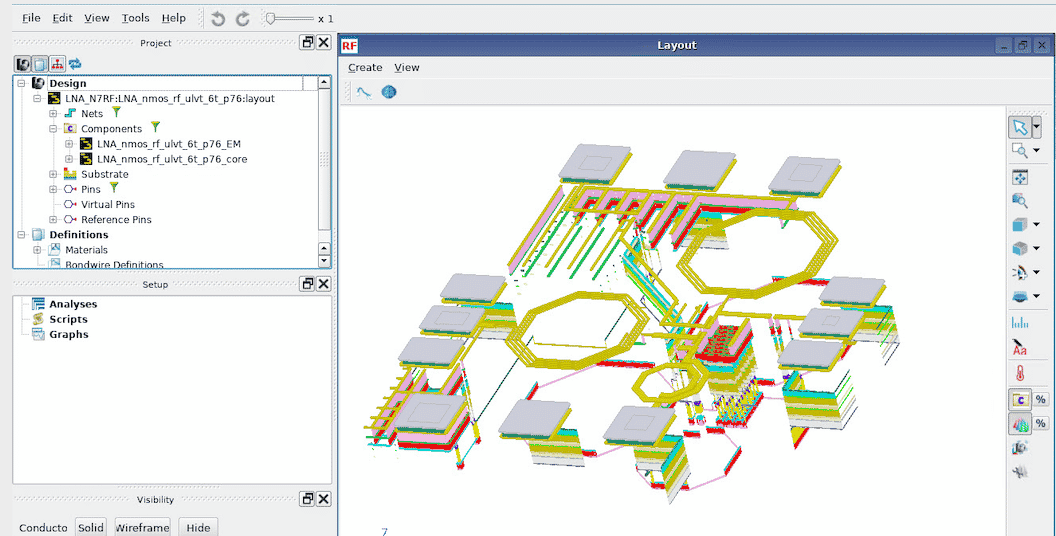

新思科技的類比流程讓客戶可以在台積公司先進的製程上,從一個節點到另一個節點發揮高效率的設計再利用。作為通過認證的EDA流程的一部分,新思科技提供可相互操作製程設計套件(iPDKs)及Synopsys IC Validator物理驗證,可實現全晶片實體簽核。

通過認證的EDA流程目前已經上市。