瑞薩科技(Renesas)日前宣布,該公司成功開發用於系統晶片(SoC)裝置的高速、低功耗、可合成式數位訊號處理器(Digital Signal Processor, DSP)核心。此DSP核心利用最新的飽和處理方法,搭配飽和預告器(Saturation Anticipator)電路,以及採用階層式結構的布局技術,使運算速度最佳化。上述先進技術,使本核心產品的速度,比瑞薩先前的DSP產品快約 20%。

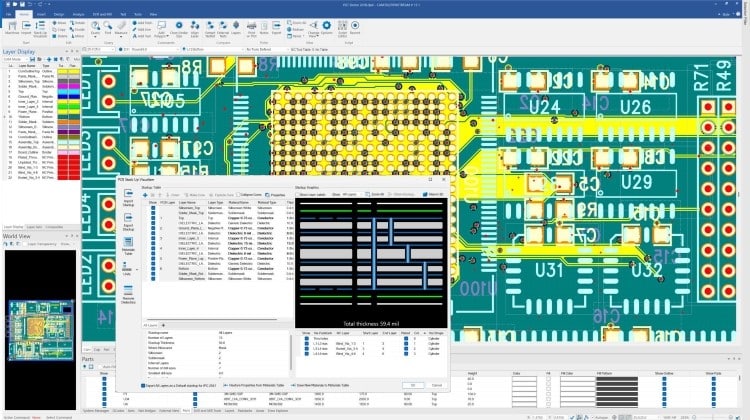

新款超長指令文字(Very Long Instruction Word, VLIW)型可合成DSP核心的測試晶片,為利用90奈米CMOS製程製造。此核心於1.2伏特電源電壓時,最高運算速率可達1.047GHz。在如此速度下進行128-tap FIR過濾運算的功耗僅有 0.10mW/MHz,且核心的矽面積極為短小,僅約0.5平方毫米。

本款DSP核心將嵌入於各種不同的瑞薩系統晶片裝置,使用在電子產品與系統的次世代多媒體處理應用。此種新核心以1GHz速度運算技術,具有以飽和預告器電路進行新型飽和作業及具階層式結構的布局技術使運算速度最佳化兩種特色,說明如下。

DSP執行大量的乘加迴圈運算,使用保護位元以避免運算時發生溢位,並提供有效率的資料處理。當DSP轉換保護位元格式的資料為無保護位元的資料時,若發生溢位,則資料會轉換為指定的最大或最小值。此飽和電路即執行偵測溢位的重要功能。瑞薩科技已開發出新型的飽和電路。

在傳統的飽和電路中,飽和運算是在加法運算完成後才執行。若飽和未遭偵測出,則飽和電路會要求運算電路的最後階段,輸出加法器產生的結果。但如果偵測到飽和狀態,則飽和電路會適時要求最後階段段輸出最大或最小值。由於上述運算必須依序逐項執行,因此無法達成高速處理作業。

傳統布局的階層式結構,是環繞功能模組而成。因此產生的關鍵路徑(Critical Path)與布線長度增加,會影響處理速度。在研發本款新DSP時,瑞薩科技分析關鍵路徑,認為其速度最為重要,於是創造一種階層式結構,使運算速度得以最佳化。最佳化的目標,則是縮短關鍵路徑的布線長度。其主要特點如關鍵路徑,並未經過數個重模組、運算單元與旁通電路(如所連結的控制線)組合成單一模組。

瑞薩科技網址:www.tw.renesas.com