賽靈思(Xilinx)宣布首度開放其新一代設計環境Vivado Design Suite,並為保固期內的ISE Design Suite客戶免費提供Vivado設計套件2012.2版本。這次全面發布分為兩階段,第一階段的目標在於加快C語言與RTL系統轉換的建置速度,而第二階段則是加速系統級的功能整合。

EVE公司執行長、總裁暨創辦人Luc Burgun表示,Vivado設計套件具備先進的布局與繞線演算法,以及精密的設計分析環境,能大幅提升設計生產力,並為EVE的產品上市時程帶來莫大的優勢。

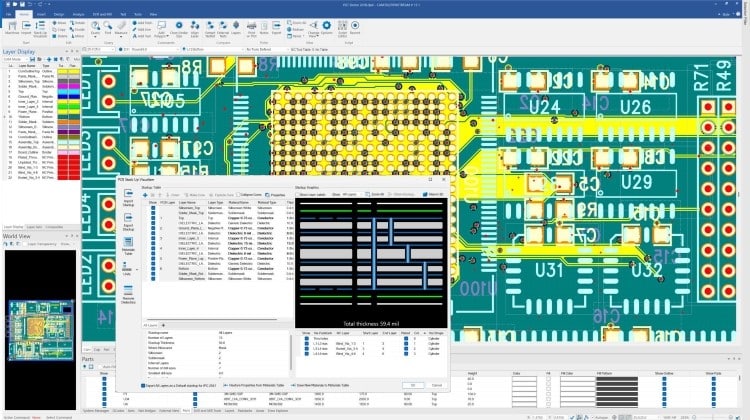

Vivado設計套件2012.2版本不僅提供一個高度整合的設計環境(IDE),更具備完整的新一代系統至晶片級(System-to-IC)設計工具,其中包括高階合成、具備業界最佳SystemVerilog支援的RTL合成、創新的分析型布局與繞線,以及以SDC為基礎的先進的時序引擎,可將建置速度提升四倍,並能協助研發業者大幅提高設計生產力。

有鑒於現今設計的規模與複雜度,研發人員面臨許多設計挑戰,常無法達到自動完成設計的目標。Vivado設計套件2012.2版本的布局與繞線技術採用各種分析技巧加快建置週期,為布線壅塞、總線路長度與時序等多重與同步設計的方法進行最佳化。

對於複雜的設計案,Vivado設計套件2012.2版本將能提升15%的效能。相較於ISE設計套件,Vivado設計套件2012.2版本在速度方面領先一個速度等級,同時和競爭元件相比,Vivado設計套件2012.2版本在中階產品系列可帶來超過三個速度等級的高效能優勢,同時在高階產品系列提供更好的的效能功耗比,更能為各系列的低成本產品帶來更佳的效能。

賽靈思延續在電子系統級(ESL)設計的領先優勢,針對所有All Programmable 7系列現場可編程閘陣列(FPGA)和Zynq-7000 EPP系統單晶片(SoC)元件推出Vivado高階合成(HLS)方案。

目前仍在保固期內的ISE Design Suite DSP Edition與System Edition的客戶可免費使用Vivado HLS。設計人員可將其C語言、C++或System C語言編寫的程式碼合成為RTL語言,為複雜的演算法快速了解各種建置架構。

Vivado HLS亦藉由建構快速模擬模型來整合系統生成工具,讓客戶快速開發視訊、成像、雷達和基頻無線電等各種應用;Vivado HLS不僅加快演算法的建置,更可將驗證時間縮短一萬倍,並可支援RTL微架構分析,藉以改進系統效能。

賽靈思網址:www.xilinx.com