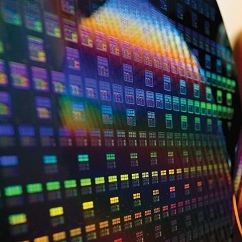

工研院揭櫫超低電壓晶片技術重大進展。工研院資通所攜手台積電、晶心科技、中正與交通大學,於25日發布超低電壓晶片技術;透過該技術所打造的晶片,操作電壓可降到0.6 V以下外,未來在應用處理器、能源管理及影像晶片設計領域將大有可為,有助台灣晶片商趕上英特爾(Intel)、德州儀器(TI)等國際大廠的研發腳步。

|

| 工研院資通所所長吳誠文認為,超低電壓晶片技術是一項兼顧「開源、節流」雙目標的最佳SoC設計方案,也會是台商站穩行動市場的關鍵。 |

工研院資通所所長吳誠文表示,低功耗設計已成晶片及系統業者在行動市場上的決勝點,誰能為設備增添續航力,就多幾分勝算;所以,台商須盡早投入相關技術布局,才有機會在行動裝置、物聯網時代中扭轉代工命運,並瓜分關鍵零組件商機。隨著工研院與產學界通力打造的超低電壓(Ultra-Low Voltage)晶片出爐,將助力台商轉型,並以國人自行研發的低電壓電路布局專利,打造各種低功耗系統單晶片(SoC),減輕每年付給國外大廠IP授權費的負擔。

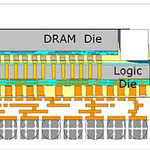

實際上,超低電壓晶片技術充滿挑戰,特別是克服低電壓製程變異極為艱鉅,故由英特爾、德州儀器等挾有豐厚研發資金的大廠,取得先占優勢。工研院資通所副所長謝明得分析,無論晶片操作電壓高低,均面臨雜訊問題,然而,大幅降低電壓後若無法同步縮減雜訊,對效能與可靠度的影響將明顯放大;此外,超低電壓晶片的核心電路雖能以0.6伏特驅動,但仍須與不同電壓的周邊電路相匹配。有鑑於此,工研院已攜手合作夥伴部署十三件專利;其中關鍵技術包含高雜訊容忍、環境變異檢測機制,以及適應性自我修復的時脈系統。

另一方面,看好超低電壓晶片往後在能源擷取的應用極具潛力,工研院也加緊布局多能源擷取系統設計、最大功率追蹤(MPPT)控制方法等五項專利。

在產學研力拱之下,工研院超電壓晶片製作流程技術已經到位,目前只欠政府或業界資金這股東風,就能導入商用量產。因此,工研院未來將積極拓展與各方合作的機會,初期將利用該方案低耗能、小體積設計優點,聚焦行動裝置、物聯網設備SoC、時脈產生器及H.264影像編解碼器開發;下一階段則將發展熱電轉換裝置、智慧監控、汽車與生醫電子等前瞻應用,持續發揮技術影響力。

謝明得補充,工研院已將該技術導入多項SoC設計,催生新一代靜態隨機存取記憶體(SRAM)、頻率產生器、影像編解碼晶片,以及太陽能/體溫能源捕捉模組等令人驚豔的低電壓、低功耗參考設計,將為台商未來在行動與物聯網市場的發展開路。