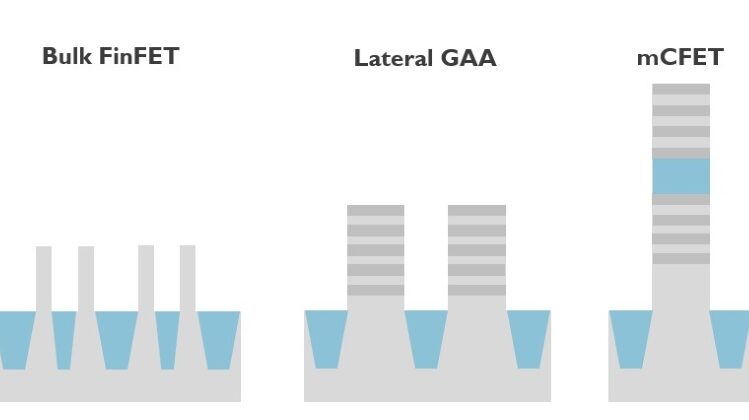

鰭式電晶體(FinFET)量產良率可望大幅提升。1x奈米FinFET製程採用嶄新3D電晶體結構、多重曝光技術,使得晶圓檢測和製程控制問題更加棘手;為此,應用材料(Applied Materials)及科磊(KLA-Tencor)等半導體設備廠近期競相發表新型晶圓、光罩及圖案成形檢測系統,期克服FinFET疊層對準、缺陷監測等挑戰,使良率達到商用量產等級。

KLA-Tencor表示,相較於傳統平面式電晶體,FinFET是極複雜的3D電晶體結構,涉及許多新的製程步驟,尤其是鰭片成形和良率問題叢生,以及伴隨著多重曝光製程而生的疊層對準、缺陷檢測等技術困難度遽增,導致各大晶圓廠導入速度不如預期;而這些挑戰亟需晶圓廠、半導體設備商和IC設計業者加強合作,發展一套製程控制策略,方能快速解決FinFET製程量產問題並提升良率。

晶圓廠當前面臨FinFET晶圓量產關鍵挑戰在於須準確測量各種參數,如鰭片側壁角度、薄膜層積厚度或圖形疊層對準誤差等資訊,以確保生產良率。此外,製程節點邁入1x奈米後,晶圓代工業者亦須因應線寬急遽微縮的情況,引進多重曝光、隔離層間距分割技術,因而也衍生更多的製程步驟及設備控制問題。

尤其在雙重曝光微影製程中,晶圓測量和製程控制系統首重層內疊層對準誤差、層間疊層對準誤差兩方面的資訊回饋,以及圖案成型分析能力。KLA-Tencor指出,該公司透過新一代電漿、雷射掃描光罩檢測系列方案,再無縫連接電子束(E-Beam)晶圓缺陷檢測系統,可掌握多層光罩的關鍵缺陷並監測良率;至於新型圖案成型控制系統則針對3D電晶體結構的多個維度、疊層對準需求,廣泛蒐集資料進行表徵、最佳化和監測,協助晶圓廠評估繁雜步驟對最終圖案的影響。

目前台積電、聯電、英特爾(Intel)和三星(Samsung)正爭分奪秒部署14/16奈米FinFET製程,新一代晶圓檢測和控制系統問世可謂及時雨,將能大幅推進FinFET商用量產腳步。

下一階段,半導體業將跨入10奈米以下FinFET製程、3D晶圓堆疊的世代,屆時晶圓檢測將更加複雜,甚至連半導體材料都可望全面換新。為搶占市場先機,應用材料近期已發布新一代物理氣相沉積(PVD)系統,以先進的可調式氮化鈦(TiN)硬式光罩技術實現10奈米以下製程的微型銅導線曝光圖像製作。

10奈米晶圓的層與層之間將有多達上百億個導孔或垂直導線,金屬硬式光罩層功用便是保持這些軟性超低電介質(ULK)中的銅導線和導孔圖形完整性;然而,隨著製程節點縮小,硬式光罩層壓縮應力使圖樣變形或倒塌的風險加劇,因此應用材料遂以可調式硬式光罩達成應力調整,以優化臨界尺寸(CD)線寬控制與導孔堆疊對位效能。

至於2.5D或3D晶圓級封裝,矽穿孔(TSV)將是不可或缺的技術,而相關挑戰包括精準測量TSV Z軸高度、TSV直徑、襯墊臨界尺和配准(Registration)等。KLA-Tencor認為,此將形成另一道晶圓檢測技術分水嶺,驅動半導體設備設計革命。