半導體業者嗅到三維晶片(3D IC)導入行動裝置的商機,紛紛投入技術研發;然而,要加速量產時程,制定邏輯與記憶體IC接合標準已成首要關鍵。因此,全球十八家晶片商正透過聯合電子裝置工程協會(JEDEC)組織委員會研擬標準,其中,日月光也投身該組織卡位3D IC封裝商機,在眾家大廠戮力推動下,該標準預計於年底定案,將協助3D IC邁開量產腳步。

|

| 日月光集團總經理暨研發長唐和明表示,3D IC猶如一幢晶片大樓,如何在既有地基向上搭建與接合仍有許多難題,因此,IC設計、晶圓代工及封測廠之間須通力合作,才能確保各個生產環節順遂無誤。 |

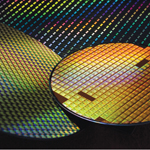

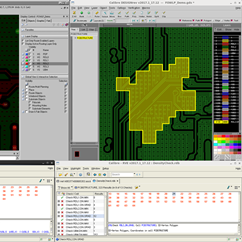

日月光集團總經理暨研發長唐和明表示,將處理器、邏輯與記憶體等異質晶片以立體堆疊形式做結合的3D IC,具有整合度高的優勢,可大幅推升運算效能,並降低耗電量及印刷電路板(PCB)占位空間,因而成為產業競相布局的新市場。然而,其設計複雜度卻遠高於傳統晶片,無論是技術及成本的挑戰皆多如繁星;其中,最大的問題在於如何接合不同類型的晶片,以及晶圓磨薄後如何精確穿孔和對位,方能打造出有效運作的立體堆疊晶片。

著眼於異質晶片接合標準對推動3D IC的重要性,唐和明透露,目前包括英特爾(Intel)、高通(Qualcomm)、博通(Broadcom)、三星(Samsung)及爾必達(Elpida)等全球十八家晶片大廠,以及掌握晶片最後一道封裝關卡的日月光已組成JEDEC JC 11.2標準委員會,快馬加鞭的推動邏輯與記憶體晶片接合的介面標準–Wide I/O Memory Bus,並可望於年底塵埃落定。如此一來,除能透過標準的依循與協助,加快廠商開發時程,促使3D IC儘早展開量產之外,並可進一步以量制價,一併解決目前3D IC生產成本居高不下的問題。

另一方面,近期半導體供應鏈加碼投資3D IC開發的現象日益顯著,包括台積電、京元電子等晶圓及封測廠均加入競逐行列,且研發費用較2010年明顯增加,對催生3D IC產品亦有推波助瀾之效。唐和明指出,樂觀來看,3D IC可望於2013年開始大量生產,應可視為3D IC的量產元年;不僅如此,若Wide I/O Memory Bus標準在年底順利過關,量產時間更可望提早至2012年底。屆時,可預見行動裝置將掀起一波兼顧高效能與超輕薄外型的產品革命。

雖然3D IC現仍處於試產階段,且並未導入實體產品設計,不過,其以矽穿孔(TSV)技術將各種晶片疊合在一起,達成高效能而低耗電的整體表現,已讓新一代的行動裝置紛紛聚焦此種晶片做為設計腹案。唐和明分析,「輕薄短小」已成行動裝置的設計圭臬,讓工程師對晶片占位空間與低功耗要求錙銖必較,促使以立體堆疊形式的3D IC漸成未來晶片主流。特別是今年各大市場研究機構頻頻上修平板電腦及智慧型手機的預估出貨量,在此一市場需求推助下,產品設計將持續朝向輕薄化邁進,而要達到此一要求,3D IC將是不可或缺的要素。

除可滿足行動裝置的設計需求外,高效能、低耗電,占位空間更小的3D IC亦可加速更新穎、劃時代的電子產品問世。唐和明強調,未來5~10年,雲端運算及物聯網(IoT)的時代將全面來臨,屆時,隨時、隨地,甚至隨「物」均須具備聯網能力。如此一來,無論是車用、醫療與生活電子皆須是聯網、輕便可攜且長時間待機等三種特性兼具的產品,若採用傳統形式的晶片勢難達成此一目標,也因此,3D IC將是引領電子產品邁向未來的關鍵。