益華電腦(Cadence)宣布台積電已選用益華解決方案,適用於20奈米設計基礎架構,其解決方案涵蓋Virtuoso客製/類比與Encounter RTL-to-Signoff平台。

益華晶片實現事業群資深副總裁徐季平表示,益華一直與台積電和雙方的客戶密切合作,開發周延的解決方案以克服20奈米設計挑戰。益華Virtuoso與Encounter 20奈米技術獨步業界且完善整合,提供一致化流程,能克服最嚴苛的低功耗混合訊號晶片的挑戰。

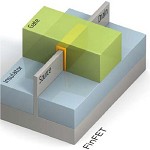

台積電採用益華技術運用於客製化設計參考製程,透過共通的技術規畫與完善整合的同步類比與數位布局,實現設計客製與數位輔助類比電路的有效方法。台積電20奈米參考製程融合Encounter與Virtuoso的全新功能與方法,兼顧新興的重要電路特性、時序收斂與設計尺寸。

對客製/類比設計人員而言,Virtuoso技術在業界標準OpenAccess資料庫中支援新的20奈米限制,包含G0規則、互動式配色實現有色彩意識的布局(Color-Aware Layout)、條件導向的預先配色流程、奇數迴路的防止與偵測(Odd-Cycle Loop Prevention)、局部互連層專屬的先進Pcell基墩(Pcell abutment)與支援。益華整合式實體驗證系統是在Virtuoso平台中整合實體驗證系統的設計技術。

對數位設計人員而言,Encounter RTL-to-GDSII支援20奈米規則、嶄新FlexColor雙重曝影(Double-Patterning)技術實現自動建構校正(Correct-by-Construction)布局與繞線,還有Encounter RTL Compiler加上Encounter數位設計實現(EDI)系統的GigaOpt最佳化,以更短的週轉時間實現更高的成品品質。

益華網址:www.cadence.com