7奈米FinFET製程技術出現新突破。新思科技(Synopsys)宣布針對台積電7奈米FinFET製程,已成功完成多項DesignWare邏輯庫及嵌入式記憶體的客戶測試晶片投片。此次投片成功意味著新思與台積電就7奈米FinFET製程在DesignWare邏輯庫、嵌入式記憶體及介面IP的合作開發上跨過重大里程碑。

台積電設計基礎架構行銷事業部資深協理Suk Lee表示,台積電與新思在先進FinFET製程上擁有長久而成功的合作關係,讓雙方共同的客戶能以最低的風險將經矽晶驗證(Silicon-proven)的高品質IP組合整合至SoC中,並讓設計人員在達成功耗、效能及面積目標上更具信心,同時加速產品上市時程。

此次合作讓新思的IP發展再添一項紀錄。藉由在台積電7奈米製程中完成多項DesignWare IP的客戶投片,該公司協助設計人員降低整合風險,且經整合的STAR記憶體系統解決方案,能達到有效率的7奈米記憶體測試(Test)及修復(Repair);同時,IP的開發實現了針對行動及高效能運算應用的第一批7奈米晶片設計。

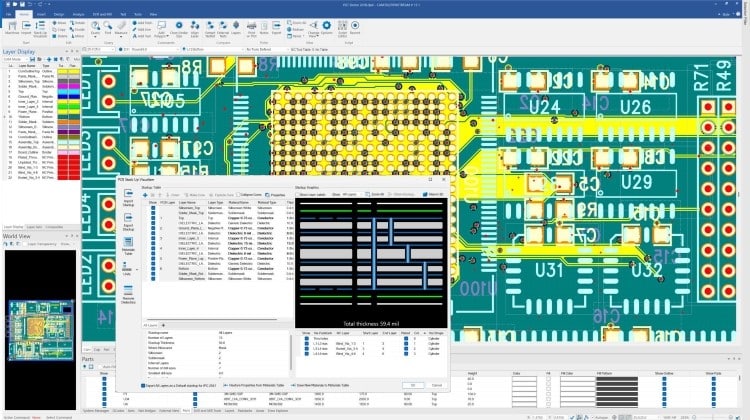

另一方面,因應7奈米製程高速運算需求,新思也與台積電合作推出針對高效能運算(High Performance Compute)平台之創新技術。新推出的創新科技含多項新的實作(Iplementation)技術,包括Design Compiler Graphical和IC Compiler II之via pillar optimization。這些新技術是由雙方合作之7奈米製程Galaxy設計平台的工具所提供,其共同開發的技術包括:通路銅柱(Via pillar)、多源樹合成(TCS)和混合時脈網格(Clock mesh),以及可配合關鍵網(Critical net)上阻力及電阻的自動化匯流排繞線(Automated bus routing)等功能。

通路銅柱是一種透過減少通路電阻與提升電子遷移(Electromigration)的強度來提高效能的新技術。Design Compiler Graphical和IC Compiler II已將通路銅柱無縫融入其流程中,包括在電路網表中插入通路銅柱、在虛擬繞線圖中模擬通路銅柱、通路銅柱的合理擺置(Legalized placement),以及支援通路銅柱的細部繞線、萃取(Extraction)和時序。

至於IC Compiler II的多源CTS和混合時脈網格在關鍵網上插入通路銅柱之後,全域(Global)與細部繞線再調整訊號繞線,以插置通路銅柱。IC Compiler II 可打造出具高客製化網格的低偏差與高效能的時脈設計,以及針對時脈進行自動H樹建置(H-tree creation)。此外,IC Compiler II也可搭配關鍵網的阻力及電阻,進行自動化的匯流排繞線,並且支援非預設(Non-default)繞線和允許使用者設定層寬度(Layer width)和間距(Spacing)。