三維晶片(3D IC)的封裝流程增添許多步驟,使製程成本加劇,為此,半導體製程設備供應商Alchimer除主打可省卻化學性機械研磨法(CMP)及黃光微影步驟,進而降低晶片與機板間導線製造成本的濕式製程外;亦針對3D IC的關鍵矽穿孔(TSV)技術,開發出高覆蓋能力的薄膜沉積(Thin Film Deposition)阻障層(Barrier)技術,大張旗鼓卡位即將成形的3D IC市場。

|

| Alchimer執行長Steve Lerner表示,Alchimer擁有獨特的半導體製程技術優勢,未來亦可望與全球製程設備、材料大廠合併,持續發揮優異製程的影響力。 |

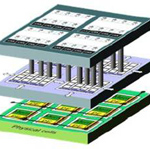

Alchimer執行長Steve Lerner表示,為實現3D IC架構須將晶圓磨得更薄,還要在晶圓上執行矽穿孔,以進行晶片間的導線互連。因此,晶片製程大翻新後,除帶來全新技術挑戰,設備與製程成本亦將攀升,而Alchimer的AquiVantage濕式製程技術,可優化矽穿孔製程後鑽孔(Via Last)方案在中介層(Interposer)、重布線層(RDL)上的導線薄膜層,提升晶圓背面導線的品質;同時也簡化整體流程,省下成本最高昂的兩道黃光微影製程,對於3D IC封裝流程帶來結構上的革新,進一步降低中介層高達50%的製造成本。

半導體濕式製程不僅可產出高品質薄膜,還可容許使用更厚的晶圓,而無需昂貴的晶圓載具(Wafer Carriers),對於化學溶液蝕刻所形成的扇形側壁表面(Scalloped Via)也能提供高度均勻覆蓋的薄膜,全面強化客戶的成本優勢。Lerner強調,AquiVantage係專為Via Last封裝製程打造,將為晶圓代工廠、封測廠(OSAT)與整合元件製造商(IDM)跨進3D IC領域帶來低成本及製程精簡的效益。

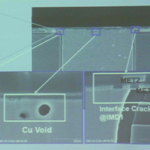

另一方面,Alchimer也透過改進薄膜沉積技術,讓矽穿孔生產更具成本效益。阻障層係矽穿孔薄膜堆疊中最底層的元素之一,而Alchimer的AquiVia阻障層製程可對複雜的矽晶圓平面提供100%階梯覆蓋率,甚至是高深寬比的扇形側壁表面,進一步突破阻障層在晶種層和填充沉積過程中,一系列與覆蓋相關的性能和可靠性問題,使後續沉積時間大幅縮短,成本亦能下探。

Lerner不諱言,傳統真空沉積製程一直無法導入高品質的阻障層,尤其是較深、直徑較小、深寬比為10:1及以上的填孔,而目前業界正亟須從這些桎梏中突圍,以全面實現3D IC整合的經濟優勢。有鑑於此,AquiVia和AquiVantage濕式製程集晶圓保形性、階梯覆蓋率和純度於一體,為物理氣相沈積(PVD)、化學氣相沈積(CVD)或其他乾式製程所不能比擬,比照標準的乾式製程可降低約40~50%的成本,將是未來3D IC的關鍵推手。

針對半導體濕式與乾式製程的比較,Lerner進一步分析,濕式製程可省卻傳統乾式製程的CMP、PVD及CVD等步驟。另對於晶片背面薄膜製程亦可選用絕緣層薄膜,而無需傳統黃光微影曝光、顯影、蝕刻與清淨的繁瑣流程,可為製程成本與營運利潤嚴密把關。此外,濕式製程除簡化整個晶圓產出流程外,更可摒除乾式製程所用設備支出及相關操作成本如真空無塵室空間、電力等,具備顯著經濟效益,不僅是切入3D IC封裝領域的絕佳考量,也是實現半導體綠色製程的關鍵拼圖。

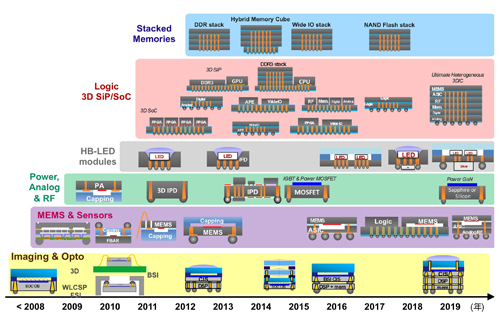

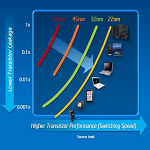

Lerner認為,3D IC可催生更輕薄且兼具高效能的產品,已成為下一代行動裝置矚目焦點;況且,在20、14奈米先進製程進展不明的情況下,3D IC亦是往下延續摩爾定律(Moore’s Law)的關鍵一著,故全球半導體業者一窩蜂投入後,市場前景隨之看俏。不過,考量到每片12吋晶圓加入矽穿孔製程後僅能增加100美元的成本,才能趨近符合終端產品採用的目標值,但現在3D IC供應鏈尚未完備,導致產出價格高於市場預期數倍。因此,預估未來兩年間供應鏈慢慢成形後,相對傳統乾式製程而言,大幅簡化流程的濕式製程將更容易達標。