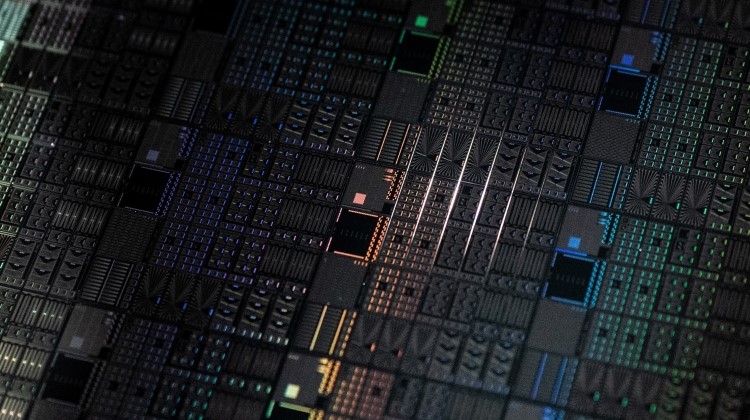

比利時微電子研究中心(imec)近日宣布,他們在12吋晶圓的矽基量子點自旋量子位元技術上取得重大進展,成功將1Hz頻率下的平均電荷雜訊降低至0.6µeV/√Hz,這是目前在12吋晶圓相容製程中所達到的最低值。這一成果顯示,12吋晶圓的量子位元製程已經成熟,未來有望實現大規模量子電腦。

基於兩大理由,矽材量子點自旋量子位元是用來實現大規模量子電腦的潛力構件。第一,矽材自旋量子位元屢次在實驗室環境中證實了其具備較長的量子相干時間(反映量子儲存資訊時間較長的指標),並能以高保真度維持量子閘運作,所以這些量子是公認且經過測試、具備現實發展前景的技術;第二,這點對長期可行性來說可能也更為重要,那就是這項潛在技術可與互補式金氧半導體(CMOS)製造技術相容,因此可能可以透過矽基量子點結構所需的先進後段製程內部互連技術,實現晶圓等級的均勻度與良率。

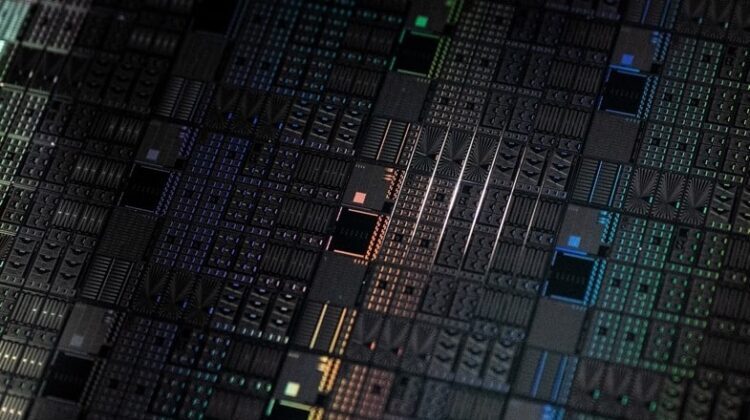

矽基量子點自旋量子位元目前有好幾種,imec目前都在進行研究。此次研究中,量子點自旋量子採用MOS量子點的結構,該結構就像是修正版的電晶體結構,用來捕獲電子或電洞的單一自旋。為提高量子位元的性能,降低電荷雜訊至關重要,因為這種雜訊會影響量子相干性。imec通過精心設計和優化12吋晶圓的製程,成功實現了顯著降低的電荷雜訊。

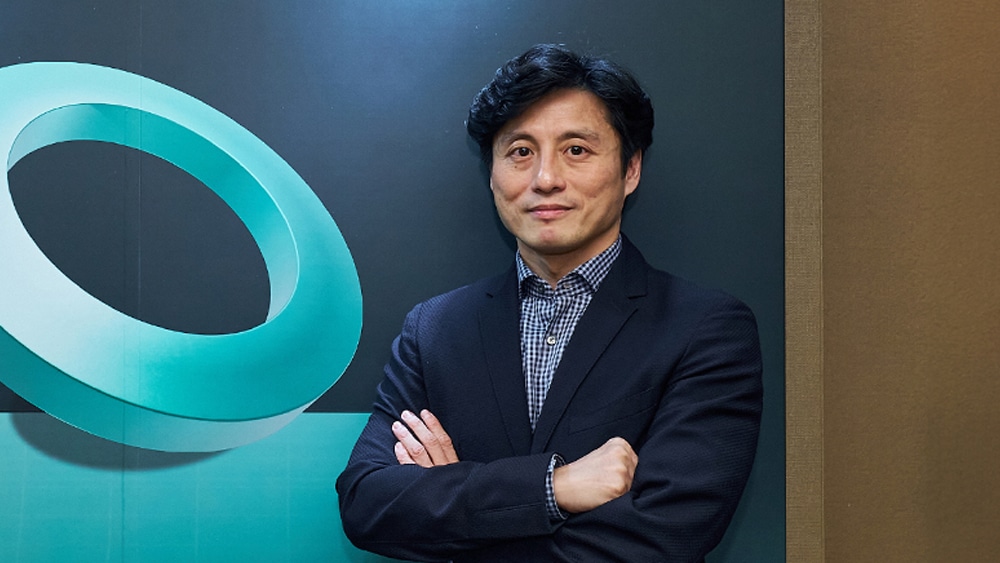

imec的量子運算研究計畫主持人Kristiaan De Greve表示,他們的研究成果顯示,與目前先進晶圓廠的矽基量子點結構相比,他們成功降低了電荷雜訊的數量級,並且量子點的運作表現一致性驚人。這些成果證實了12吋晶圓矽基MOS設計在量子位元製造中的可靠性,顯示出量子位元開發技術的成熟度。

此外,研究團隊還利用統計分析方法深入了解電荷雜訊的來源,這將有助於進一步優化量子點結構。De Greve強調,具備低雜訊的量子位元環境和CMOS製造技術的均勻性,僅僅是推動量子晶片升級的起點,最終目標是實現應用量子運算,這需要數以百萬計的量子位元。

這項研究成果已發表於Nature Partner Journals期刊。