英特爾(Intel)與工研院攜手開發的三維(3D)動態隨機存取記憶體(DRAM),已進入晶片試產(Tape Out)階段,未來將可望挾超高性價比優勢,橫掃行動裝置與雲端資料中心等應用。

|

| 英特爾副總裁暨實驗室執行總監王文漢表示,英特爾實驗室在台推動的多項計畫,皆已達成重要里程碑。 |

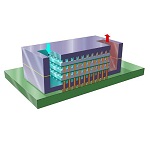

英特爾實驗室副總裁暨執行總監王文漢表示,現在是DRAM產業世代交替的一個時間點,各種創新技術發展的機會也相對蓬勃。英特爾實驗室和工研院從2011年開始合作進行研究,針對未來的超輕薄筆電(Ultrabook)、平板電腦、智慧型手機等行動裝置,以及未來的百萬兆級(Exascale)與超大型雲端資料中心(Cloud Mega Datacenter)成功開發高效能且超省電的陣列記憶體架構。

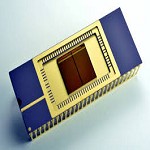

王文漢進一步指出,這項合作計畫已開發出多款低功耗實驗性陣列記憶體(Experimental Memory Array),以及一款原型陣列記憶體產品。原型陣列記憶體運用矽穿孔(Through Silicon Via, TSV)技術堆疊成3D的立體結構,不僅提升3D堆疊與系統最佳化的成效,且可以讓高密度記憶體大幅改善記憶體的電源使用效益並提高成本效益。

事實上,英特爾打造低價3D DRAM優勢的重要關鍵係一款DRAM區域/供電/時序模型建構工具(DRAM Area, poweR and Timing, DArT),為針對3D DRAM所設計的模擬器,用來分析數以千計的陣列結構。

王文漢強調,DRAM的改造須要進行全面性的架構分析,以因應頻寬成長與降低延遲的需求,而DArT模擬工具可用在陣列組建以及介面客製化方面的應用。透過適當的設計抽象化,英特爾與工研院的組件式模型建構法能提供更高的彈性與精準度,讓DArT適合用來探測DRAM架構以及預測效能。

王文漢指出,與既有的混合記憶體立方體(Hybrid Memory Cube, HMC)方案相較,英特爾與工研院攜手開發出的3D DRAM方案除具備低占位面積、超低耗電、高資料接取速度及超高容量等優勢外,更重要的是在價格上有十足的競爭力,因此可大幅度滲透各式行動裝置及需要高容量的雲端資料中心應用。

據悉,目前戮力研發3D DRAM方案的業者除英特爾、工研院外,美光、三星(Samsung)亦投入大量資源於研發工作中,其中,美光已於今年11月宣布將於千兆級(Petascale)超級運算系統中導入旗下混合記憶體立方體方案,同樣採用TSV技術,最高可達160GB/s的記憶體頻寬,且較現有記憶體方案省下70%功耗,預計2014年後開始量產。