縮小電路的線寬雖有利於提高電晶體效能,但導體的線寬越細,反而會使電阻增加,拖累晶片效能並增加功耗。若無法在材料工程方面有所突破,從7奈米節點縮到3奈米節點,導線通路電阻將增加10倍,反而失去電晶體微縮本應帶來的好處。為克服此一物理瓶頸,美商應材(Applied Materials)推出一種嶄新的布線工程設計方法,能促使先進邏輯晶片的線寬微縮到3奈米,甚至更小尺寸。

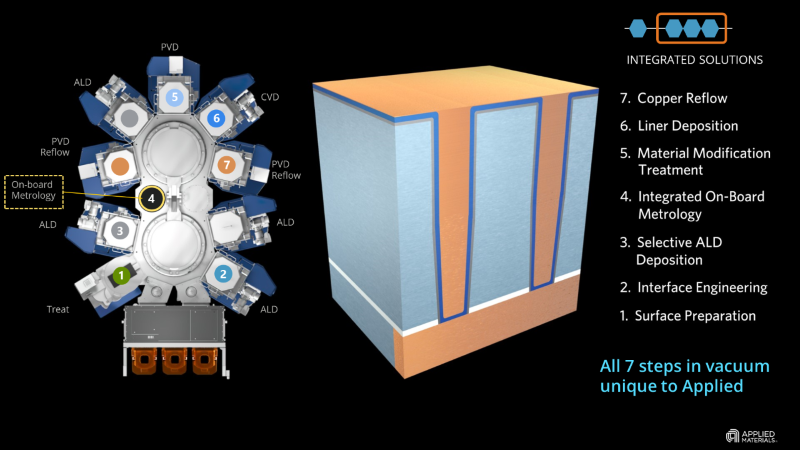

應材已開發出一種名為銅阻障層晶種整合性材料解決方案(Endura Copper Barrier Seed IMS)的全新材料工程解決方案。這是一項整合式材料解決方案,在高真空環境下將七種不同製程技術整合在一套系統中,這七種技術分別是:原子層沉積(ALD)、物理氣相沉積(PVD)、化學氣相沉積(CVD)、銅回流、表面處理、介面工程和量測。該組合使用選擇性ALD取代共形ALD,消除通路介面處的高電阻率阻障層。這項解決方案還加入銅回流技術,在狹窄特徵中實現無空隙填充。

由於通路接觸介面的電阻減少50%,可明顯提升晶片效能和降低功耗,故半導體製造廠可以將邏輯晶片的線寬微縮到3奈米甚至更小尺寸,不必擔心線寬變細所帶來的副作用。

應材資深副總裁暨半導體產品事業群總經理Prabu Raja表示,一顆智慧型手機晶片內含數百億條銅導線,光是布線所消耗的功率預算,就已占整顆晶片的三分之一。在真空中整合多種製程技術,讓我們能夠重製材料和結構,讓消費者擁有功能更強大的裝置及更長的電池使用時間。這項獨特的整合解決方案是專為協助客戶加快發展效能、功率和面積成本的技術藍圖。