CMOS射頻(RF)元件壯大發展聲勢。CMOS RF藉矽材料/製程成本低、產能充足等優勢,持續瓜分傳統砷化鎵(GaAs)、矽鍺(SiGe)RF市占;近期,芯科實驗室(Silicon Labs)更發動新一波市場攻勢,率先推出CMOS RF數位接收器單晶片,提供媲美傳統RF元件的效能,並減輕數位無線電(Digital Radio)系統占位空間及物料成本,有助CMOS RF陣營持續擴張勢力。

|

| 芯科實驗室副總裁暨廣播產品總經理James Stansberry提到,處理器整合CMOS RF的設計備受期待,但因大量數位雜訊將影響RF效能,仍須3~5年發展才可望實現。 |

芯科實驗室副總裁暨廣播產品總經理James Stansberry表示,數位無線電科技可大幅提升廣播音訊品質並傳送更多資訊予使用者,將開啟廣播事業新視野,然而,相關系統仍受制於零組件用量龐大、高成本及高耗電等RF設計問題,而延宕市場發展腳步。為改善此弊病,借重互補式金屬氧化物半導體(CMOS)RF的功能特色與生產優勢已是業界共同努力目標。

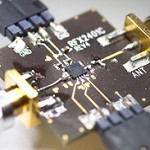

其中,芯科實驗室日前已利用CMOS RF與軟體定義無線電(SDR)技術,搶先業界發布新一代數位接收器單晶片,透過整合低雜訊放大器(LNA)、低壓差線性穩壓器(LDO)、自動增益控制(AGC)和數位訊號處理器(DSP)等大量零組件,可在不損及RF性能與效率的前提下,大幅改進體積與功耗。此外,還可透過SDR功能完整支援調頻(FM)、高音質廣播(HD Radio)和數位音訊廣播(DAB)/DAB+等標準,全面提升RF系統價值,以加速數位無線電應用普及。

Stansberry指出,由於CMOS技術能提高RF周邊元件整合度,將使消費性電子、行動裝置內部RF系統減輕物料清單(BOM)成本及耗電量。以RF數位接收器為例,CMOS RF單晶片較傳統兩塊印刷電路板(PCB)分離式RF設計,大幅縮減80%占位空間及50%以上成本;同時還能結合各種類比元件與數位校正機制,優化RF高頻效率、動態電壓範圍和抗雜訊能力,補強CMOS製程材料先天特性不佳的缺陷。

事實上,CMOS製程不僅可降低RF元件生產難度,在擴產方面也相對材料特殊的砷化鎵方案容易,甚至能與基頻處理器、記憶體等元件整合為單一系統單晶片(SoC),因而被視為RF產業新星。

Stansberry強調,隨著消費性電子、行動裝置支援更多無線功能、體積與厚度不斷縮小且出貨量急遽擴大,其內部RF系統設計成本及尺寸也須持續微縮,且要有充備的產能才能滿足市場要求。也因此,近來各種消費性或可攜式電子導入CMOS RF的需求已顯著攀升,包括電視調諧器(TV Tuner)、AM/FM發射器與接收器等均快速轉向CMOS RF設計。未來CMOS RF應用更將持續往無線區域網路(Wi-Fi)、3G/4G功率放大器(PA)邁進,搶占更多行動裝置RF設計商機。