業界首顆64位元系統單晶片(SoC)現場可編程閘陣列(FPGA)搶先亮相。Altera宣布將以英特爾(Intel)14奈米(nm)三閘極(Tri-gate)製程推出Stratix 10系統單晶片FPGA,採用四核心、64位元安謀國際(ARM)Cortex-A53處理器,以及浮點數位訊號處理器(DSP)及高效能FPGA結構,期大舉進攻資料中心加速運算、雷達系統及通訊設備等應用市場。

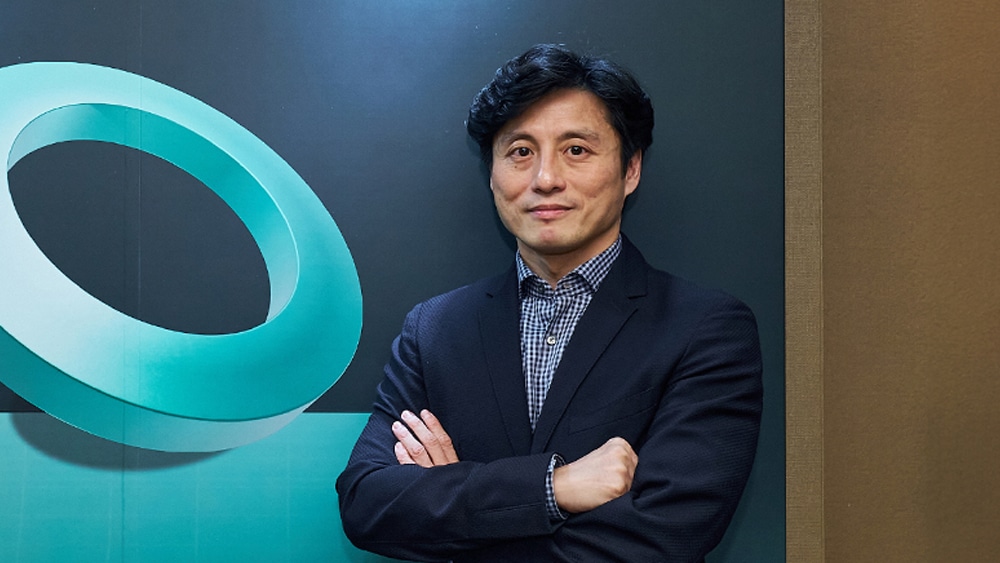

Altera企業策略與行銷資深副總裁Danny Biran表示,對客戶而言,高整合度元件將持續成為複雜、高效能應用產品的最佳解決方案;而Stratix 10 SoC能讓工程師擁有一個多功能且效能強大的異質(Heterogeneous)運算平台,讓他們可以設計出更創新且更快上市的產品。

ARM處理器部門執行副總裁暨總經理Tom Cronk指出,Cortex-A53處理器可提供高效率功耗及理想的表現效能,且ARM生態系統及軟體社群將全面支援該顆處理器,因此Altera以最低功耗的64位元架構補強DSP與FPGA運算元素,將可創造出最先進的異質運算平台。

事實上,ARM Cortex-A53處理器係第一顆被SoC FPGA採用的64位元處理器。Altera將其應用於Stratix 10 SoC,看重的是Cortex-A53處理器的效能、功耗及數據吞吐量及其他先進特色。Cortex-A53係目前ARM應用層級處理器中具備最高電源效率的產品,不僅如此,Cortex-A53在英特爾14奈米Tri-Gate製程的助力下,將可提供較現今最高效能的SoC FPGA六倍以上的數據吞吐量。

除效能外,Cortex-A53處理器亦提供虛擬支援功能,包括256TB記憶體及在L1及L2快取(Cache)的錯誤校正碼(ECC)。此外,Cortex-A53處理器核心可以32位元模式運作,亦即以Cortex-A9運作系統執行且軟體相容,該特色將可讓Altera的28奈米及20奈米SoC FPGA無縫升級。

Altera提高Stratix 10 SoC效能表現的關鍵,除採用Cortex-A53處理器架構外,英特爾14奈米Tri-Gate製程亦扮演要角。Altera Stratix 10 SoC將可提供高於1GHz的可編程邏輯效能,相當於現今28奈米製程FPGA的兩倍,並降低70%的耗電量。除此之外,Stratix 10 SoC內建業界首創硬體浮點運算DSP區塊,可提供每秒十兆次的浮點運算(10TFLOPS)效能。

Altera在第一代及第二代的SoC產品線中已導入ARM Cortex-A9 MPCore核心,而在第三代SoC產品–Stratix 10 SoC,Altera更延續一貫風格,以Cortex-A53核心做為提高SoC FPGA效能的重要武器,因此,該公司將提供一系列設計軟體及ARM生態系統工具及作業系統支援,包括以Altera版本的ARM DS-5開發工具為特色的SoC嵌入式設計套件(EDS),以及Altera的OpenCL軟體開發套件(SDK),期協助工程師利用OpenCL高階設計語言完成異質運算平台,並縮短開發時間。