Silego展開穿戴式電子市場首波攻勢。看好穿戴式電子市場成長前景,Silego發表極薄矩形平面無接腳封裝(Extreme Thin DFN, ETDFN)方案–Lo-Z,欲以僅0.27毫米(mm)的厚度以及超低功耗的優勢,推出一系列可配置混合訊號積體電路(Configurable Mixed-signal IC, CMIC),全面攻占穿戴式電子市場版圖。

|

| Silego行銷總監Nathan John指出,採用Lo-Z封裝技術方案將為客戶帶來較分離式元件方案更低的功耗以及更佳的散熱表現。 |

Silego行銷總監Nathan John表示,傳統印刷電路板(PCB)元件配置方式往往受限於主動式元件(Active Circuit)與被動式元件(Passive Circuit)的厚度、體積不同,因此廠商常將雙方分別放置於PCB的兩側,但若主動式元件廠商導入Lo-Z技術,即可讓產品以僅0.27毫米的高度與被動元件放置於同一側,並縮小整體電路板面積及厚度,而如此一來,手持式裝置及穿戴式電子製造商將可開拓更多的外觀尺寸(Form Factor)可能性。

John強調,與晶圓級晶片尺寸封裝(WLCSP)技術相較,Lo-Z封裝技術可以為客戶減少二分之一以上的產品厚度,且Lo-Z封裝提供額外的環境光(Ambient Light)保護並可以避免WLCSP常發生的破裂問題。

Silego總裁暨執行長Ilbok Lee指出,Lo-Z封裝首波鎖定的應用市場為穿戴式電子及運動健身手表,緊接著是軟性顯示器(Flexible Display)及射頻(RF)模組市場,至於智慧型手機、平板及筆記型電腦亦將是該技術可著墨的重要領域。

Lee認為,穿戴式電子市場變化甚鉅,客戶在極短的生命週期內欲創造差異化產品,將傾向於採用可編程方案,卻同時具備高成本壓力,因此Silego於業界創造CMIC分類,期結合類比元件與類似現場可程式邏輯閘陣列(FPGA)的架構,樹立「可編程類比元件」標準,同時提供特殊應用積體電路(ASIC)的成本競爭力與FPGA的設計彈性,預期CMIC事業可為該公司帶來至少3億美元的潛在營收。

事實上,由於一級(Tie1)客戶對CMIC需求若渴,2009~2013年Silego旗下CMIC事業營收年複合成長率(CAGR)高達46%;而今年CMIC出貨量已達五億顆,為該公司挹注近5,000萬美元的營收。

John透露,Silego的Lo-Z封裝技術已獲得穿戴式電子主要大廠的青睞,未來將應用於運動健身手表、手環等應用市場,且該公司極有自信可以ETDFN封裝技術奪下更多的大單,為Silego創造倍數成長的營收。

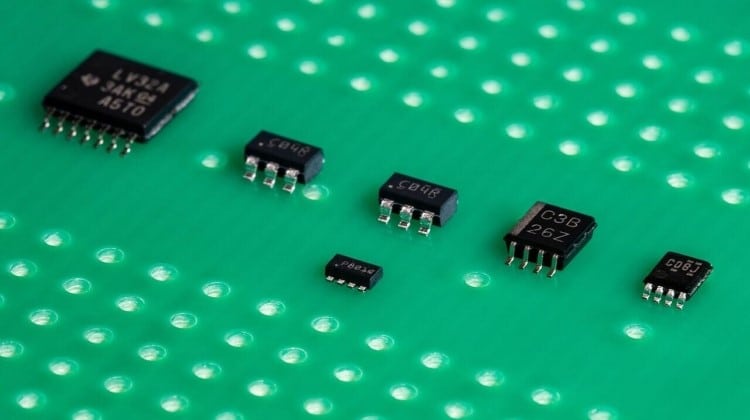

Silego已搶先於旗下電源切換器(Load Switch)– SLG59M1493Z GreenFET3系列產品導入Lo-Z封裝技術。SLG59M1493Z係八接腳單通道電源切換器,尺寸大小僅1.0毫米×1.6毫米×0.27毫米。未來該公司計畫將Lo-Z封裝技術導入旗下其他產品線,包括GPAK可編程混合訊號矩陣(GPAK Programmable Mixed-signal Matrix)與GCLK 32.768 kHz石英晶體替代產品系列。