台灣半導體產業鏈正積極研發三維晶片(3D IC)新材料。由於3D IC引起一連串晶圓製程變革,帶動各種新興半導體黏著、填充材料需求;台灣半導體晶圓廠、研究單位、設備及材料商正研擬共同開發計畫,期突破關鍵材料掌握在歐、美、日外商手中的桎梏,強化3D IC量產技術獨特性並改善成本結構。

|

| 工研院材化所高寬頻先進構裝材料研究室研究員鄭志龍提到,台商在晶圓永久性接合與底層填充材料方面發展較成熟,是搶進3D IC商機的最佳途徑。 |

工研院材化所高寬頻先進構裝材料研究室研究員鄭志龍表示,3D IC帶來劃時代的改變,須透過矽穿孔(TSV)技術鑿穿晶圓並填入導電金屬,隨後執行晶圓薄化(Wafer Thinning)、晶圓接合(Wafer Bonding)動作。在製程大幅改變之下,包括光阻、電鍍、介電層(Dielectric Layer)、底膠填充(Underfill)、晶圓暫時與永久性黏著等材料也須跟著革新。

鄭志龍指出,台積電在3D IC發展,已逐漸跳脫以往直接選用日本半導體材料大廠產品製作晶圓的框架,正積極轉向與國內材料業者、設備廠合作研發獨特機台與材料配套方案,讓旗下3D IC製程標新領異,並達成提升量產效率及降低成本降低等目標。

除產業界醞釀組織3D IC聯軍外,經濟部工業局亦著眼於市場對3D IC製程材料的強烈需求,進一步祭出半導體材料專案補貼計畫,期招攬更多業者加入新一代3D IC材料開發行列,推進量產時程以搶占市場先機。

鄭志龍透露,台灣過去在先進半導體材料較少著墨,主要貨源來自外商;然而,看好3D IC將引爆新的發展契機,遂激勵國內業者相繼投入新材料研究。包括長興化工、長春石化和肥特補等半導體材料供應商,皆已加碼研產3D IC晶圓接合、底膠填充材料。而工研院材化所亦揭櫫穿透度、彎折性更佳的3D IC永久接著材料,並致力串連晶圓代工、設備與材料端業者,推行產業共同開發計畫。

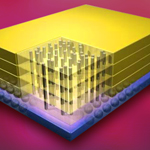

據了解,3D IC最重要的矽穿孔製程,成本耗費來源主要集中在孔洞填充(Via Filling)部分,比例高達40%;其次則為晶圓接合階段,占比35%,是降低3D IC成本的兩大關鍵。鄭志龍分析,進行孔洞填充前須鍍上介電絕緣層和種子層(Seed Layer),相關材料目前僅美國羅門哈斯(Rohm and Haas)、樂思化學(Enthone)及阿托科技(Atotech)可供應,台商仍須一段時間發展。

至於晶圓接合方面則須改良錫球接合技術,並導入具高黏性、快速散熱特性的底層填充材料。鄭志龍認為,底層填充材料與設備依存度高,未來產業垂直整合將蔚為風潮;值此台灣半導體產業共同開發計畫如火如荼開展之際,將使材料商在未來3D IC製造領域發揮更強大的戰力。目前國內業者已開始發展具高散熱效能、低硬化溫度及感光能力的多功能底層填充材料,可望迎頭趕上國際大廠。

另外,為了讓半成品晶圓貼合在特殊載具上磨薄時不會移位,3D IC晶圓薄化製程亦須採用暫時黏著材料,且須「黏得緊,剝得乾淨」,才能確保製作良率及品質,技術門檻較高。目前全球僅TMAT(Thin Materials AG)、3M、杜邦(Dupont)、東京應用化學(TOK)及Brewer Science五家半導體材料商推出相關方案。