聯華電子正式加入14奈米(nm)鰭式場效電晶體(FinFET)製程戰局。聯電與新思科技(Synopsys)於日前宣布,兩家公司的合作已獲得初步成果;聯電採用新思科技DesignWare邏輯庫矽智財(IP)組合和Galaxy實作平台StarRC寄生參數提取工具,成功完成聯電第一個14奈米FinFET製程驗證工具設計定案。

聯電市場行銷副總郭天全表示,此次設計定案的成功,是聯電技術研發的重要里程碑,聯電的目標是提供客戶高競爭力的FinFET技術解決方案,協助客戶產品走在技術前端。聯電選擇新思科技做為此次重要合作夥伴,原因在於新思科技在FinFET領域的專業,以及在先進製程開發DesignWare矽智財的豐富經驗。此次合作成果將可大大嘉惠積體電路(IC)設計公司,為客戶帶來功耗、效能、成本等各面向的產品競爭力。

新思科技矽智財與系統行銷副總John Koeter表示,新思科技致力於開發開發通過驗證的FinFET矽智財與IC設計工具,可協助聯電認證關鍵製程和矽智財測試結構,藉此降低IC設計公司整合產品的風險,並且加速其產品的量產時程。

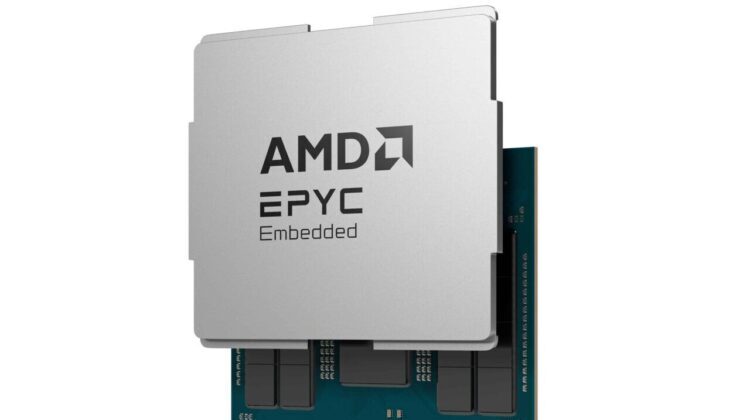

據了解,聯電將在2015年量產首批產品,緊追英特爾(Intel)及台積電的腳步。事實上,由於FinFET製程具備高效能、低功耗以及比平面互補式金屬氧化物半導體(CMOS)製程較低的數據保留電壓等優勢,因而成為IC設計公司高度重視的先進製程節點。

新思科技製程驗證工具將提供初期數據,讓聯電得以調整其14奈米FinFET製程,藉以得到最佳化功耗、性能和裸晶(Die)面積。同時,新思科技驗證工具也提供製程檢視數據,讓聯電FinFET模擬模型與矽製程結果具更高關聯性。