比利時微電子研究中心(IMEC)正全速開發下世代10奈米製程技術。為協助半導體產業跨越10奈米鰭式電晶體(FinFET)製程技術門檻,IMEC已啟動新一代電晶體通道材料和電路互連(Interconnect)研究計畫,將以矽鍺/三五族材料替代矽方案,並透過奈米線(Nanowire)或石墨烯技術實現更細緻的電路成型與布局,加速10奈米以下製程問世。

|

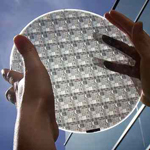

| IMEC製程科技副總裁An Steegen提到,除了10奈米以下製程技術外,IMEC亦全力推動18吋晶圓的發展,目前已有相關設備進入驗證階段。 |

IMEC製程科技副總裁An Steegen表示,目前16/14奈米FinFET技術成熟度已達到一定水準,全球主要晶圓代工廠均預計在2014~2015年投入量產;然而,下一階段的10奈米技術則尚未明朗,原因在於電晶體通道大幅微縮後,傳統矽材料將面臨物理極限,使晶圓廠無法顯著提升晶片效能;加上電晶體密度激增,相關業者亦須改良製造工具,以及電路布局(Layout)的設計規範(Design Rule)和製程設計套件(PDK),勢將增添量產製程發展的不確定性。

Steegen強調,為繼續往下延伸摩爾定律(Moore’s Law),半導體供應鏈業者和技術研究單位正密切投入開發新一代半導體材料、設備、電路成型及布局方案。其中,IMEC已將電子移動性較佳的矽鍺(SiGe)、鍺、鎵(Ga)或三五族(III-V)化合物列為矽材料的優先替代選項,從而在電晶體通道愈趨緊密的前提下,持續提升電子驅動性能。

據悉,10奈米FinFET製程對設備、材料和臨界尺度(Critical Dimension)控制等各方面都將帶來新的要求,但尤以新材料研究較難掌握、耗時且影響層面大;因此IMEC遂將其視為布局重點,並於日前在日本舉行的2013年超大型積體電路(VLSI)國際會議中,發表可應用於10奈米以下製程的鍺/矽鍺淺溝槽隔離(STI)方案,進而改善矽通道效能及可靠度不佳的問題。

此外,FinFET轉向立體架構,晶圓廠為確保良率,亦須嚴格掌控離子擴散狀況;對此,IMEC則以特殊探針(Probe),開發類似電子顯微鏡的SSRM(Scanning Spreading Resistance Microscopy)方案,並提供相關機台設計支援與代測服務,讓晶圓廠更精確掌握離子擴散時的細微變化與不良情形。

與此同時,IMEC亦從微影、電路成型和布局方案著手,期協助晶圓廠克服10奈米以下製程極其緊密的布線挑戰。Steegen透露,針對10或7奈米製程方案,IMEC將採用奈米線或石墨烯電路互連技術,實現更細緻的電路布局;目前正與晶圓廠合作夥伴攜手定義新的設計規範和PDK,最快可望在7奈米製程導入奈米線,開啟半導體技術發展新頁。

至於微影技術方面,IMEC正與艾司摩爾(ASML)致力於新世代極紫外光(EUV)微影機台的驗證,從而以單次曝光(Single-patterning)的形式,協助晶圓廠減輕多重曝光(Multiple-patterning)的昂貴成本,使10奈米以下量產製程更具經濟效益。Steegen指出,ASML每一版研發型EUV機台都會優先提供予IMEC測試,該公司預計於今年底推出的最新設備亦將在近期進駐IMEC,進行細部調整與優化,以配合10奈米製程的研發腳步。