超低電壓MEMS時脈元件將成業界新寵。隨著傳統石英振盪器逐漸難以因應行動裝置輕薄、低功耗設計需求,業界已轉向運用標準化半導體製程研發微機電系統(MEMS)振盪器、超低電壓無石英(Crystal-less)時脈產生器;近期,工研院更積極融合兩種技術優點,進一步打造高精準度、低耗電與小尺寸時脈元件,以滿足行動裝置日益嚴苛的設計要求。

|

| 工研院資通所低功耗混合訊號部技術副理李瑜提到,無石英時脈產生器最大優勢在於可與矽晶片完全整合,故多以IP形式搶攻成熟且訴求低價的中低階時脈應用市場。 |

工研院資通所低功耗混合訊號部技術副理李瑜表示,目前市面上有三種時脈元件解決方案,分別是石英振盪器、MEMS振盪器及無石英時脈產生器。在行動裝置嚴格要求低功耗、輕薄化的影響下,傳統石英振盪器因須採用金屬或陶瓷封裝,不僅生產成本較高、交貨期間長,且難微縮封裝尺寸與高度,地位已漸漸式微;相較之下,MEMS振盪器及無石英時脈產生器則快速崛起,開始瓜分行動裝置市場商機。

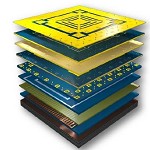

其中,MEMS振盪器雖擁有尺寸微縮、精準度媲美石英振盪器的優勢,但內部包含前端MEMS諧振器與後端補償電路,囿於晶圓製程變異與MEMS元件特性,仍面臨單價高、溫度及電壓適應力弱等問題;同時,其驅動電壓仍在1.8~3.3伏特(V)之間,要縮減功耗滿足行動裝置需求,就須導入更多省電機制,影響系統效能與成本。因此,工研院提出MEMS諧振器整合超低電壓電路的解決方案,全力克服上述問題。

李瑜透露,工研院日前發布超低電壓晶片技術,將與MEMS振盪器進一步結合,催生更高整合度、低耗電時脈元件。現階段,資通所與南分院正緊鑼密鼓展開新產品研發計畫,將整合MEMS諧振器,以及一顆基於0.3~0.5伏特(V)超低電壓補償電路製成的特定應用積體電路(ASIC),兼容前者的高精準度、高頻率穩定性,以及後者的低電壓驅動、適應溫度範圍等優點。

李瑜分析,MEMS振盪器相容半導體製程與封裝技術,極具尺寸微縮、晶片整合度、量產速度與成本等效益,且頻率精準度平均已達到10~20ppm以下,滿足中高階時脈應用產品規格;未來整合超低電壓補償電路後,更有助改善MEMS振盪器操作環境變異、時脈穩定度問題,提供更出色的效能修復機制,並降低50%以上功耗。

此外,利用經驗證、優化的超低電壓晶片技術,亦可減輕MEMS振盪器在晶圓層級、功能性及溫度測試的複雜度,從而壓縮測試時間與成本,更快達成降價目的,以加速取代石英振盪器。

不僅如此,MEMS廠也開始醞釀行動系統單晶片(SoC)內建MEMS振盪器的解決方案,以去除外部時脈電路,達到提升效能與降低成本的雙重功效。李瑜認為,這是MEMS振盪器的獨特設計優勢,有助其壓低單價並快速提高滲透率,進而擴大取代石英產品;反觀石英元件封裝形式與SoC則不相容,無法達成該設計需求。

至於無石英時脈產生器方面的進展,工研院亦已開發一款超低電壓時脈產生器,除尺寸非常微小外,亦將功耗控制在12微瓦(µW)以下,並達到±500ppm精準度水準,可望在中低階時脈應用領域快速擴張版圖。

顯而易見,傳統石英振盪器正面臨左右夾攻的局面;為扳回一城,相關供應鏈業者已著手改良石英時脈元件的封裝技術,甚至進一步投入測試可匹配半導體製程的生產方案,期大幅縮減尺寸與成本,防堵MEMS、超低電壓時脈產生器的強力攻勢。