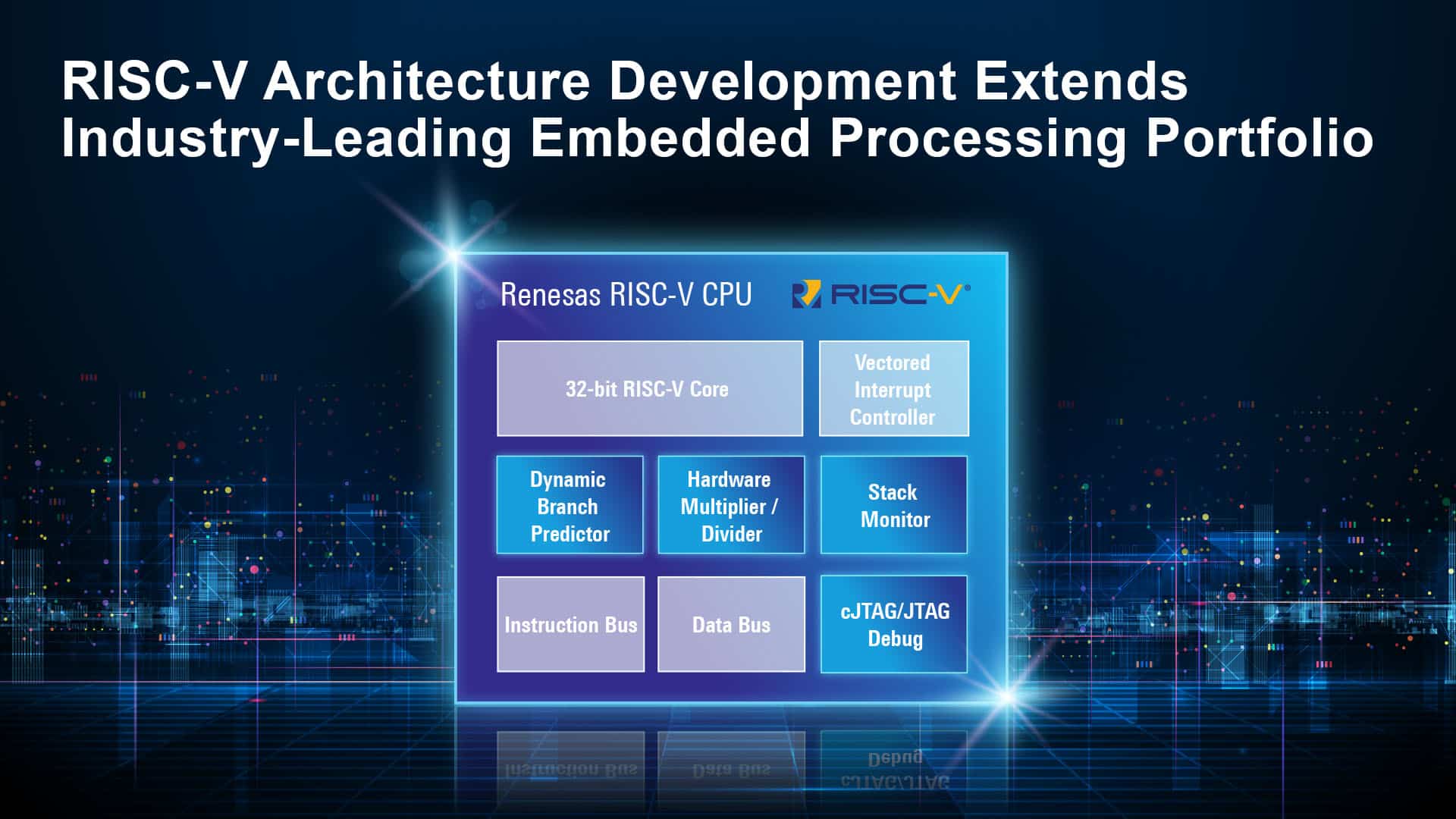

瑞薩電子宣布推出基於64位RISC-V CPU內核心的RZ/Five通用微處理器(MPU)RZ/Five採用Andes AX45MP,基於RISC-V CPU指令集架構(ISA),增強了瑞薩現有基於Arm CPU內核的MPU陣容,擴充了客戶的選擇,並在產品開發過程中提供更大靈活性。

瑞薩電子物聯網及基礎設施事業本部SoC事業部部長、高級副總裁新田啟人表示,高興瑞薩能夠成為首批推出Andes 64位RISC-V CPU內核心通用MPU產品的企業之一。隨著RZ/Five MPU的發布以及生態系統的支持,瑞薩在提供理想的RISC-V解決方案方面已先行一步。

RZ/Five針對這一需求進行了優化,可提供物聯網終端設備所需的性能和外圍功能。產品最大工作頻率為1 GHz。其外圍功能包括對多個接口(如兩個千兆以太網通道、兩個USB 2.0通道和兩個CAN通道)的支持和雙A/D轉換器模組。同時還支持連接具有錯誤檢查與糾正(ECC)及安全功能的外部DDR存儲器。

與RZ/G系列一樣,RZ/Five也可使用具有(CIP)Civil Infrastructure PlatformLinux內核心且經驗證的Linux軟件包(VLP)。CIP作為一款工業級Linux,提供超過10年的長期維護支持。這使得RZ/Five系列成為需要高可靠性與更長服務壽命的企業基礎設施和工業領域應用的理想產品。此外,它還使得用戶可大幅縮減未來的Linux維護成本。

RZ/Five的外圍功能和封裝與基於Arm內核的RZ/G2UL產品相兼容,可靈活重複使用經過驗證的設計。RZ/Five還採用更小、更緊湊的封裝,以更有效地滿足複雜度較低的設計。作為評估環境,RZ SMARC評估板套件將配備一個符合SMARC 2.1標準的模塊板(等同於目前RZ/G系列的評估環境)。該套件允許在RZ/Five CPU模塊和RZ/G2UL CPU模塊間進行切換及評估,使評估變得更為輕鬆,並縮短產品開發週期。