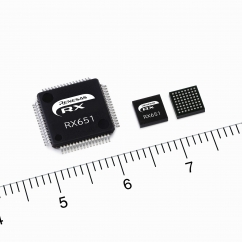

瑞薩(Renesas)發表系統級封裝(SiP)Top-Down設計環境之開發作業,可在開發時提升效率,將多個晶片如系統單晶片(SoC)裝置、微控制器(MCU)及記憶體等結合至單一封裝。此設計環境採用由上向下(預測型)設計方式,可在設計的初始階段檢查各項關鍵特性,如設計品質及散熱等。

SiP Top-Down設計環境整合並最佳化多項工具,包括可整合至SiP產品中的晶片資訊資料庫及基板布局工具。此環境提供可在設計工具間傳送資料的使用者介面,以提升易用性與彈性,並提供可自動執行作業的設計環境,例如在電路模擬時進行分析。由於具備上述先進功能,將可在初始設計階段針對可能大幅影響開發新SiP所需時間的項目執行檢測作業,如分析電子特性以確保訊號品質(Signal Integrity)及散熱功能的熱分析等。結果將可提升設計品質並使開發時程減半。

SiP Top-Down設計環境之主要功能特色為整合多種工具之設計資料庫及通用使用者介面;於設計初始階段執行大規模封裝基板雜訊分析,考量基板布局的散熱分析

瑞薩計畫將SiP Top-Down設計環境的應用擴大至各種SiP產品的開發,並將持續建立開發解決方案以因應客戶最新的需求。

瑞薩網址:www.renesas.com