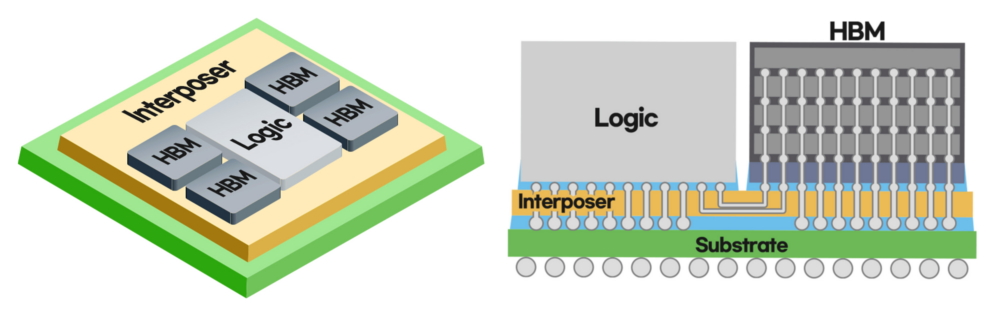

三星(Samsung)新一代的2.5D封裝技術Interposer-Cube4 (I-Cube4)即將上市,承接I-Cube的異質整合技術,可將多個邏輯晶粒(Logic Die),包含CPU、GPU等,以及高頻寬記憶體(HBM)晶粒放置到矽中介板(Silicon Interposer)上,因此多個晶粒的運作起來像是一個封裝中只有一個晶片。

I-Cube4是I-Cube2的下一代,具有四個HBM及一個邏輯晶粒。I-Cube4可望滿足高效能運算(HPC)、人工智慧(AI)、5G、雲端及大規模資料中心應用的需求,透過邏輯電路與記憶體的異質整合,帶來速度更快的通訊及較高的節能效果。 三星晶圓代工廠市場策略資深副總裁Moonsoo Kang表示,隨著高效能應用程式的爆炸式成長,提供代工廠異質整合技術,可以增加晶片整體的效能並降低功耗。借助I-Cube2的量產經驗及I-Cube4突破商業目標,三星將持續支援客戶的產品規劃。

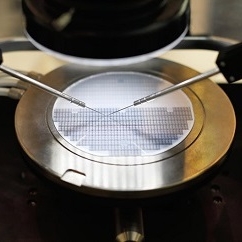

通常矽中介板需要增加面積以容納更多邏輯晶粒及HBM,而I-Cube的矽中介層比紙張更薄,僅有大約100㎛,因此大面積的中介層較容易產生彎曲或翹曲,造成負面影響。為此,三星透過改變材料及厚度,研發控制中介層翹曲和熱膨脹的技術,實現I-Cube4的商業化。

此外,三星為I-Cube4開發無模具結構,移除熱量的同時,在製造時預先篩選出有瑕疵的產品,藉此提高產量。此方法可以減少製造流程,進而節省成本並縮短處理時間(Turnaround Time)。

在2018年推出I-Cube2及2020年推出eXtended-Cube (X-Cube),可說是三星在高效能運算市場的里程碑。近期三星將結合高階處理節點、高速傳輸介面IP及2.5/3D封裝,為I-Cube6開發更多高階封裝技術,協助客戶提高產品開發效率。