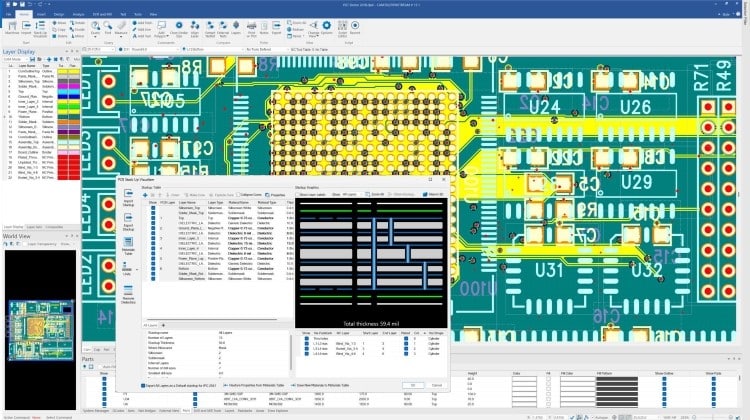

益華電腦發表的Palladium XP II驗證運算平台,奠基於Palladium XP仿真技術,擴展容量達二十三億邏輯閘,大幅提升驗證效能達50%,加速軟體驗證,為強化系統開發套裝不可或缺的一環。由於更低的功耗與更高的閘道密度,半導體與系統製造廠商現在能夠以更小的面積承載更大的資料量,讓產品上市時間提前4個月,驗證生產力提高兩倍。

GSEDA首席分析師Gary Smith表示,全新升級的Palladium XP II平台硬體功能以及更先進的使用模式,讓益華能夠克服使用者所面對、從系統到驗證逐漸攀升的嚴苛挑戰。

有鑑於及早、快速且精準的軟硬體驗證需求不斷地增高,益華以Palladium為核心,擴大系統開發套裝的功能,包括專利申請中的混合式技術,結合益華虛擬系統平台(Virtual System Platform)與Palladium XP系列,提高嵌入式操作系統(OS)驗證速度達六十倍,以及軟硬體驗證效能達十倍;此外還包括先進系統虛擬化環境的嵌入式測試程式,讓使用者能夠在投入試產之前驗證周邊驅動程式,加速晶片系統級的開發與驗證。

輝達(NVIDIA)工程協理Narendra Konda指出,受益於益華電腦Palladium虛擬系統平台混合式解決方案,輝達在電路仿真(In-circuit Emulation)時能夠享受Palladium平台帶來高達六十倍的OS啟動速度,並在OS上執行量產與測試軟體時達十倍的效能提升,且能夠與精準的硬體設計互動。這種新的使用模式大幅縮短輝達的系統軟體驗證時間,並確保更順暢的晶片開發與驗證。

益華電腦網址:www.cadence.com