益華電腦(Cadence)發表新一代設計實現解決方案系–Innovus,讓系統單晶片(SoC)開發人員能提供具備同級最佳功耗、效能與面積(PPA)設計,同時加速上市前置時間。此方案系統在16/14/10奈米(nm)鰭式電晶體(FinFET)和成熟製程上,一般能提升10~20%的功耗、效能與面積生產力優勢,同時整個流程速度與產能可提高5~10倍。

Cadence數位與Signoff事業群資深副總裁Anirudh Devgan表示,客戶已開始使用該設計實現系統,達成更高效能、更低功耗與最小面積。在量產設計上早期部署這項解決方案的客戶表示PPA獲得大幅改善,周轉時間也明顯加速。

該設計實現系統大幅縮短每次繞線與布局循環的周轉時間,其核心演算法已經過多重執行緒技術的強化,在擁有八到十六顆中央處理器(CPU)標準硬體上實現大幅加速。此外,該系統還具備大規模分散式平行解決方案,支援一千萬及以上的處理程序設計區塊,即使面對多重模式、多環境差異性情境,仍能加速執行。

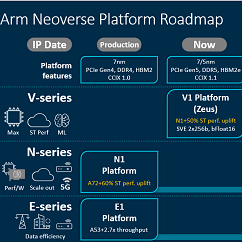

安謀國際(ARM)CPU事業群總經理Noel Hurley指出,ARM不斷推進晶片與電子設計自動化(EDA)工具技術極限,在緊迫時程內提供產品,滿足消費性產品市場需求,其中Cortex-A72處理器時運用Innovus設計實現系統,不僅加快五倍執行速度,同時在面積目標內實現超過2.6GHz的性能。

益華電腦網址:www.cadence.com