益華電腦(Cadence Design Systems)宣布與台積電簽署一份為期多年的協議,針對行動、網路架構、伺服器與現場可編程閘陣列(FPGA)應用軟體的先進製程設計,開發16奈米鰭式電晶體(FinFET)技術專屬設計基礎架構。這項深度合作在設計流程中比一般更早的階段便已展開,將有效解決FinFET專屬的設計挑戰。

益華電腦晶片實現事業群資深副總裁徐季平表示,建立這種複雜、開創性製程所需的設計基礎架構,需要晶圓廠與電子設計自動化(EDA)廠商間的密切協作。與台積電合作,益華電腦貢獻獨家技術創新與專業,為設計人員提供所需的FinFET設計功能,讓高效能、具備電源效率的產品順利上市。

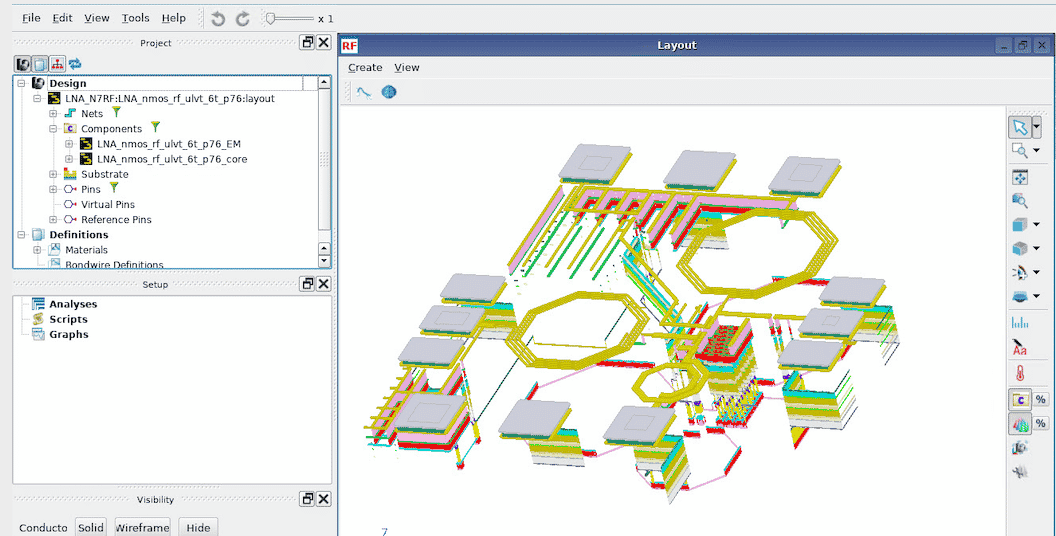

FinFET有助於提供功耗、效能與面積(PPA)優勢,這是在16奈米和以下製程技術開發高度與眾不同系統單晶片(SoC)設計的必備要項。與一般平面電晶體截然不同,FinFET採用從基底突出的垂直鰭狀結構,眾多閘極包裹在鰭的上方與周圍,產生許多具備低洩漏電流與快速交換效能的電晶體。

益華電腦網址:www.cadence.com