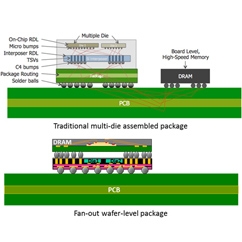

益華電腦(Cadence)宣布旗下系統級封裝(Allegro SiP)和實體驗證系統(PVS)實現技術已能完整支援台積公司(TSMC)的整合型扇出型(InFO)封裝技術。透過提供可自動化設計規則檢查(DRC)流程的整合式解決方案,Allegro SiP設計軟體工具和PVS可協助台積公司客戶縮短InFO的設計與驗證週期。

Cadence PCB部門產品管理總監Keith Felton表示,隨著行動與IoT應用的需求成長,市場對於先進封裝技術的要求也跟著提高。結合該公司自有的IC封裝設計與IC實體驗證專業技術,以及與台積公司的合作經驗,讓該公司成功開發出特定的InFO布局與驗證特性,以滿足設計時的製造需求,因此能縮短設計週期並加快上市時程。

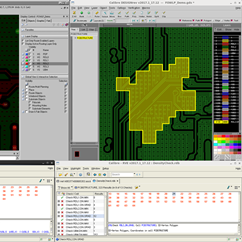

在與台積公司合作實現InFO技術時,益華為Allegro SiP Layout開發新的IC封裝技術,以滿足InFO的特定設計需求,並為設計人員提供多項特性,符合並確認InFO設計的設計規則、布局結構與金屬密度要求。此外,益華也量身打造光罩產生(Mask-generation)技術,能以GDSII格式準確地表示InFO設計結構,讓設計人員能先確認光罩的準確度,才將資料提交給台積電進行製造。

台積公司設計基礎架構行銷事業部資深協理Suk Lee表示,此整合式工具流程能將IC封裝設計與IC製造兩個領域銜接在一起,將能讓該公司成功地全面部署InFO封裝技術。

益華網址:www.cadence.com