物聯網應用開枝散葉,帶動少量多樣設計需求,包括Google、亞馬遜(Amazon)、鴻海和小米等大廠相繼投入自有系統單晶片(SoC)研發,形成新的無晶片(Chipless)商業模式,不僅擠壓無晶圓廠(Fabless)晶片商發展空間,也將牽動晶圓代工、矽智財(IP)、電子設計工具自動化(EDA)及IC設計服務商市場戰略轉變。

|

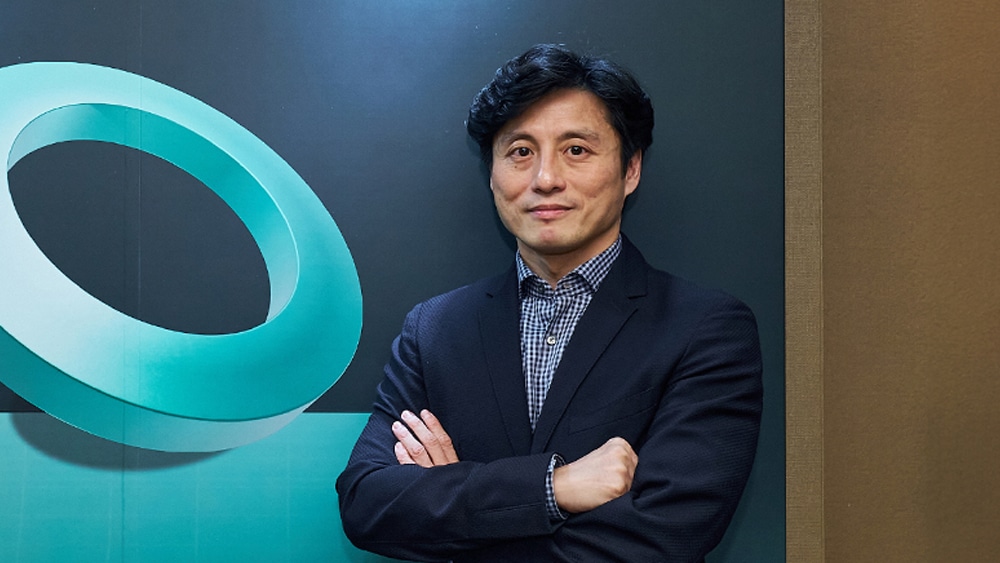

| Cadence資深副總裁暨策略長徐季平認為,未來幾年半導體產業將出現巨大變革,將為EDA廠商帶來更多機會。 |

益華電腦(Cadence)資深副總裁暨策略長徐季平表示,半導體產業正走向10奈米以下節點,以及強調超低功耗、類比混合訊號(Analog Mixed Signal)的物聯網IC製程發展分水嶺。先進製程方面,鰭式電晶體(FinFET)、多重曝光(Multiple Patterning)皆使晶圓生產面臨更艱鉅的層間互連(Interconnect)、製程控制和位移(Shift Left)運算難題。然而,物聯網IC則有更多挑戰跳脫技術範疇,著重於「少量多樣」的設計流程、產業鏈合作等層面,甚至將牽動商業模式轉變,創造繼IDM、Fabless之後的第三種勢力。

Cadence台灣區總經理張郁禮補充,家庭、醫療、汽車和工業物聯網應用迸發,但各產業皆有獨特要求不可能以通用型晶片解決,因此半導體產業開始興起Chipless新商業模式,可望翻轉既有開發流程,反過來從系統整合、軟體應用面回推晶片架構、製程及效能需求;尤其近來Google、亞馬遜、鴻海和小米等廠商競相發展自有系統單晶片,或攜手EDA、IC設計服務商打造特定晶片的風潮,更加助長Chipless成形。

隨著先進製程的投片、驗證成本飆高,Fabless晶片商整併態勢已無可避免,方能創造足夠的規模支撐網路基礎設施和行動裝置SoC研發花費。相較之下,基於成熟製程節點、晶片架構精簡,但訴求少量多樣設計彈性的物聯網IC則適合Chipless發展模式,未來可望吸引更多系統廠或應用服務商湧進布局,刺激晶圓代工、IP、EDA和IC設計服務業者聯手搶攻。

由此可見,物聯網時勢造英雄,Chipless商業模式已引發半導體業新化學效應。據悉,聯電近期與旗下轉投資IC設計服務公司–智原即共同發表55奈米嵌入式快閃記憶體(eFlash)製程,瞄準物聯網和穿戴式裝置晶片設計商機。與此同時,安謀國際(ARM)、Imagination也不約而同發展IP子系統(Sub-system)平台,整合物聯網所需的嵌入式處理器、無線通訊、資料介面等IP,以及安全防護軟體或作業系統,以加速壯大物聯網SoC市場規模。

張郁禮更透露,以往Cadence大多鎖定晶圓代工廠、IP供應商和IC設計公司為合作對象,但近期已開始出現系統廠客戶,其中尤以中國大陸廠商最為活躍;因此該公司開始調整戰略,朝更全面的SoC開發解決方案供應商角色邁進,除提供完整的數位邏輯EDA工具支援外,亦針對特定領域開發軟體,如汽車功能安全(Functional Safety)模擬器(Simulator),以及各種數位輔助類比(Digital Assisted Analog, DAA)設計工具,同時透過顧問服務加強與客戶在設計流程上的合作,讓非IC設計領域的廠商都能快速投入開發SoC。