思源宣布推出第三代自動化積體電路(IC)設計偵錯平台–Verdi 3。為協助IC設計廠商提升IC偵錯效率,新版偵錯平台具備自定功能、客製化操作環境以及高效率資料存取等特色,可讓工程師達到縮減設計時程與降低開發成本的目的,克服現今日趨複雜的IC設計與驗證挑戰。

|

| 思源科技營運長鄧強生表示,Verdi 3的偵錯效率在先進製程IC設計開發時,尤為顯著。 |

思源科技營運長鄧強生表示,由於28及20等先進奈米(nm)製程即將成為主流,IC電晶體數量隨著半導體製程縮減不斷增加,造成原有偵錯平台已逐漸不敷IC設計廠商在進行偵錯、驗證工作時的效率要求。因此,電子設計自動化(EDA)廠商除必須提供客戶效能更高的偵錯解決方案,也須提供符合使用者自身需求的客製化功能及使用者圖形介面(GUI)加速偵錯作業流程,以利客戶產品儘早面市,搶占市場先機。

鄧強生進一步指出,為解決上述問題,思源推出新一代自動化IC設計偵錯產品–Verdi 3,可支援多執行緒(Multi-threaded)的快速訊號資料庫(FSDB)讀取、更精簡的FSDB儲存檔案與併時邏輯模擬檔案寫出(Parallel Logic Simulation Dumping)等功能,可較前一代Verdi版本節省近50%的設計時程以及降低30%的檔案寫出大小,加速客戶對28奈米產品的偵錯速度。

除強化資料存取速度外,Verdi 3亦提供全新的人機介面以及客製化功能,讓使用者更易於使用該平台。Verdi 3採用基於QT使用者圖形介面,不僅可讓原本在偵錯過程中須要開啟好幾個視窗的操作行為,簡化為單一視窗,還可任意變更視窗中的工具設定或新增自定命令(Command)、視窗工具列以及快捷鍵,提升使用者操作效率。

另一方面,Verdi 3亦可與思源去年於10月所推動的VIA開放式平台做緊密整合,以擴大偵錯工具選項。使用者可在Verdi 3的圖形介面中直接執行VIA所編寫的功能,為自身的偵錯流程設定量身訂做的應用程式,以滿足不同公司的設計流程需求。

鄧強生透露,現今全球已有包括德州儀器(TI)、瑞薩電子(Renesas Electronics)以及聯發科等四十多家IC設計廠商相繼採用Verdi 3。未來亦將會有更多的Verdi客戶升級為此最新版本,以因應半導體先進製程所帶來的新挑戰。

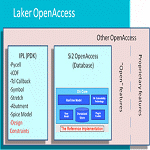

相較於新思(Synopsys)、益華(Cadence Design)以及明導國際(Mentor Graphics)等EDA廠商較著重於後段EDA的研發,思源則主要專注於前段的偵錯功能,其Verdi系列產品於全球已有五成以上的市占率,並占該公司整體營收60%。鄧強生指出,除Verdi 3外,思源今年內亦將發表新版客製化IC設計解決方案–Laker平台,進一步擴大整體營收。