USB4將傳輸速率由20Gbps提升到40Gbps,而高速傳輸也將帶來幾項挑戰,包括:訊號干擾與傳輸損耗,因此在電路板設計布局、連接器與纜線設計等都更為要求,必須透過嚴謹的系統化整合設計,協助維持高速傳輸訊號的完整性。

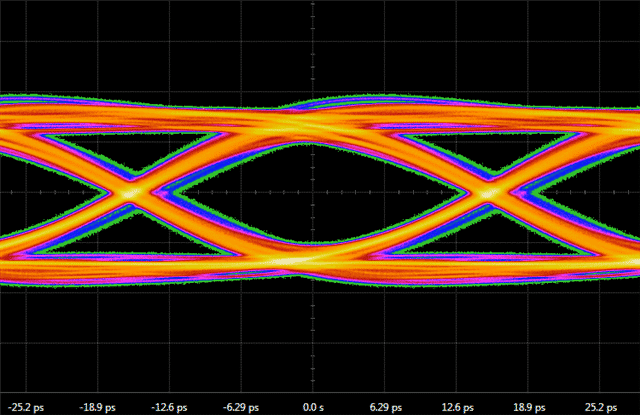

現今有線高速傳輸提速的技術大多透過多通道與差分訊號來達成,差分訊號對的傳輸也由低頻傳輸升級為高頻傳輸。維將科技總經理鍾軒禾表示,高頻差動訊號對訊號品質的好壞,最直接的影響是訊號對本身的粗細厚薄與距離,而間接的影響是共模雜訊,電路設計不良時,將因此產生電磁輻射造成電磁干擾(EMI),甚至是與其他無線電訊號發生共振而造成射頻干擾(RFI)。

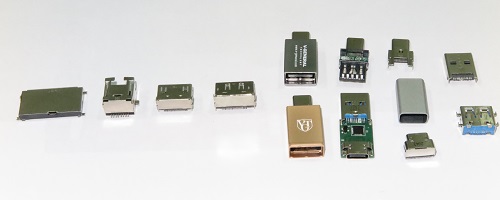

鍾軒禾形容,連接器是有線通訊中重要的水閥,要改善有線連接中的干擾狀況甚至訊號傳輸損失,需要將纜線、連接器、電路板當作一個系統進行整合性設計,讓訊號傳輸的過程可以最順暢,只要透過機構設計的調整,就可以有效解決訊號的干擾與耗損問題,無須用到重計時器(Retimer)與中繼器(Redriver),整體系統成本不升反降。

過去纜線、連接器、電路板是由不同的廠商負責,不僅各做各的,在遭遇問題時也容易互踢皮球,在高速傳輸中,每一段的匹配與連續性都非常重要,只要一個部分出現問題,整體系統的效能就會大打折扣,所以不僅纜線、連接器、電路板,甚至控制晶片都需要整體性的設計,才有助於問題的解決。

而只要高頻連接器引腳的電性排序位置重新設計定義,鍾軒禾認為,透過單排設計,高頻差分訊號對兩側有參考邊避免串音干擾其他訊號,並將高頻訊號對的導體加粗減少訊號衰減,從接觸端一直到控制晶片的引腳都有參考邊,所以訊號完整性就會更好。雖然在纜線、連接器與電路板上的成本會較高,但因為少了重計時器與中繼器,整體系統成本並不會增加。