四核心晶片戰火愈來愈猛烈。有別於市面上四核心處理器多半採大核加小核的設計架構,聯發科、ST-Ericsson最新四核心方案相繼改走差異路線,前者押寶Cortex-A7核心,讓晶片運算效能既可媲美同級產品,又能大幅降低耗電量與尺寸;後者則導入新處理器架構並應用意法半導體(ST)獨特28奈米製程,以實現動態調整CPU電壓及頻率,使效能與功耗均衡發展。

工研院IEK系統IC與製程研究部研究員蔡金坤表示,為兼顧行動裝置效能與功耗,包括安謀國際(ARM),以及輝達(NVIDIA)、德州儀器(TI)等晶片商紛紛開發整合大、小核心的四核系統單晶片(SoC)。此類架構雖為目前四核方案主流,但卻要求完善的中央處理器(CPU)切換、SoC電源管理機制,因而也帶來諸多技術挑戰,加重晶片商投資負擔。

蔡金坤進一步分析,利用大核加小核設計架構,雖可讓CPU各司其職,並滿足行動裝置高效能與低功耗運算需求,但也容易使得SoC內部電路架構變得複雜,增加待機功耗問題;所以須從改良SoC架構著手,擴充核心數目才有價值。

也因此,聯發科、ST-Ericsson遂另闢發展蹊徑,催生不一樣的四核心晶片。以聚焦中國大陸市場的聯發科為例,即採用Cortex-A7核心及28奈米(nm)製程,打造小尺寸、低功耗四核心方案,可提供較一般Cortex-A9四核處理器更高的性價比。

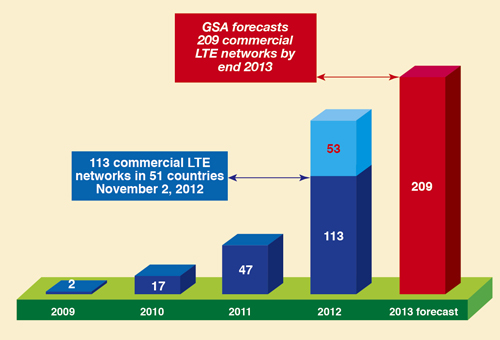

至於ST-Ericsson則在2013年國際消費性電子展(CES)展上,揭櫫旗下最新四核心行動SoC–NovaThor L8540 LTE ModAp。為在市場上後發先至,該公司除整合應用處理器與長程演進計畫(LTE)多頻多模數據機外,並透過28奈米完全空乏型矽絕緣層金氧半電晶體元件(FD-SOI)製程,開發高效率四核心SoC設計架構–eQuad,使內部各個CPU具備電壓和頻率動態調整(DVFS)功能,並可在高驅動電壓、最高時脈2.5GHz,以及0.6伏特(V)超低電壓、800MHz時脈兩種模式下運作。

ST-Ericsson已計畫於2013年第一季推出四核SoC樣品,協助手機品牌廠開發支援LTE Category 4規範、WUXGA(1920×1200)顯示與超低耗電規格的高階行動裝置。ST-Ericsson總裁暨執行長Didier Lamouche表示,利用28奈米FD-SOI高效能、低漏電製程,該晶片可在不犧牲SoC整體效能的情況下,滿足業界對延長行動裝置續航力的殷切需求,將為整個行動產業發展帶來重大突破。