在台積電(TSMC)2024年北美技術研討會上,西門子數位工業軟體宣佈針對台積電最新和最先進的製程技術成功實現多項產品認證,雙方合作專案亦達到重要里程碑。這些認證幫助雙方共同客戶運用EDA軟體和矽製程及先進封裝技術,實現持續創新,並開發具有差異性的終端產品。

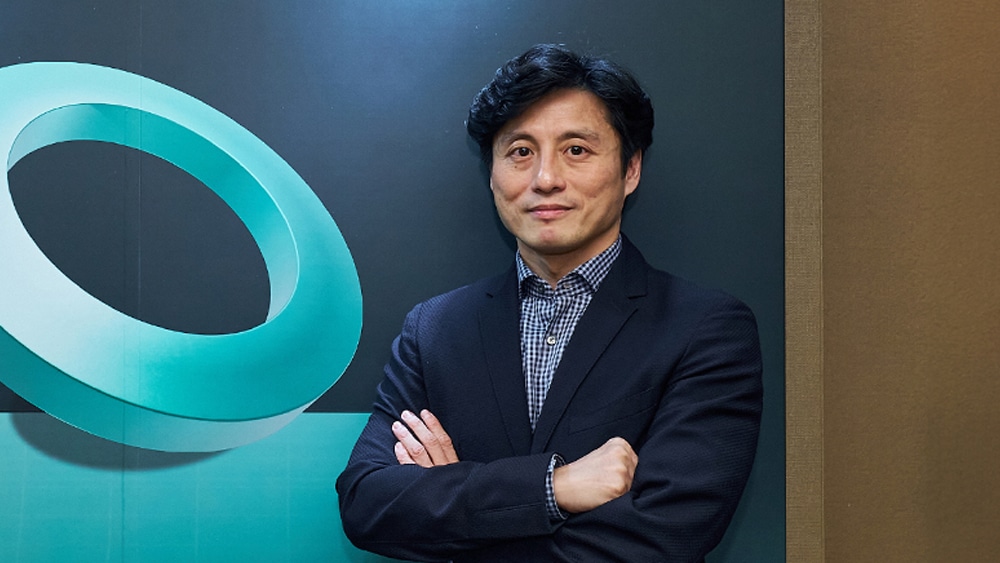

西門子數位工業軟體電子設計自動化執行副總裁Mike Ellow表示,西門子與台積電合作提供EDA技術,使客戶即便在時間、成本和設計複雜性的壓力不斷升高的今天,仍然可以擁有多樣且高效的設計途徑。西門子的IC設計解決方案,搭配台積電尖端的製程與先進封裝技術,可以幫助客戶實現真正卓越的、顛覆產業的創新。

西門子的Calibre nmPlatform平台是IC驗證的工具,其現已通過台積電N2製程認證。Calibre其他通過N2認證的工具組還包括:西門子的Calibre nmDRC軟體、Calibre nmLVS軟體、Calibre Pattern Matching軟體和Calibre PERC軟體,所有工具現在都可以提供給台積電創新技術的早期使用者使用。

西門子的Analog FastSPICE平台用於為奈米級類比、無線射頻、混合式訊號、記憶體和客製化數位電路提供電路驗證,近期也已獲得台積電的N3P、N2和N2P先進製程認證。此外,西門子的Analog FastSPICE平台作為台積電N2製程客製化設計參考流程(CDRF)的一部分,現在也可支援台積電的可靠性感知模擬技術,可解決IC老化和即時自體發熱效應,並提供其他進階的可靠性功能。台積電N2技術的CDRF也包含西門子的Solido Design Environment軟體,可用於在高sigma下進行進階變異感知驗證。

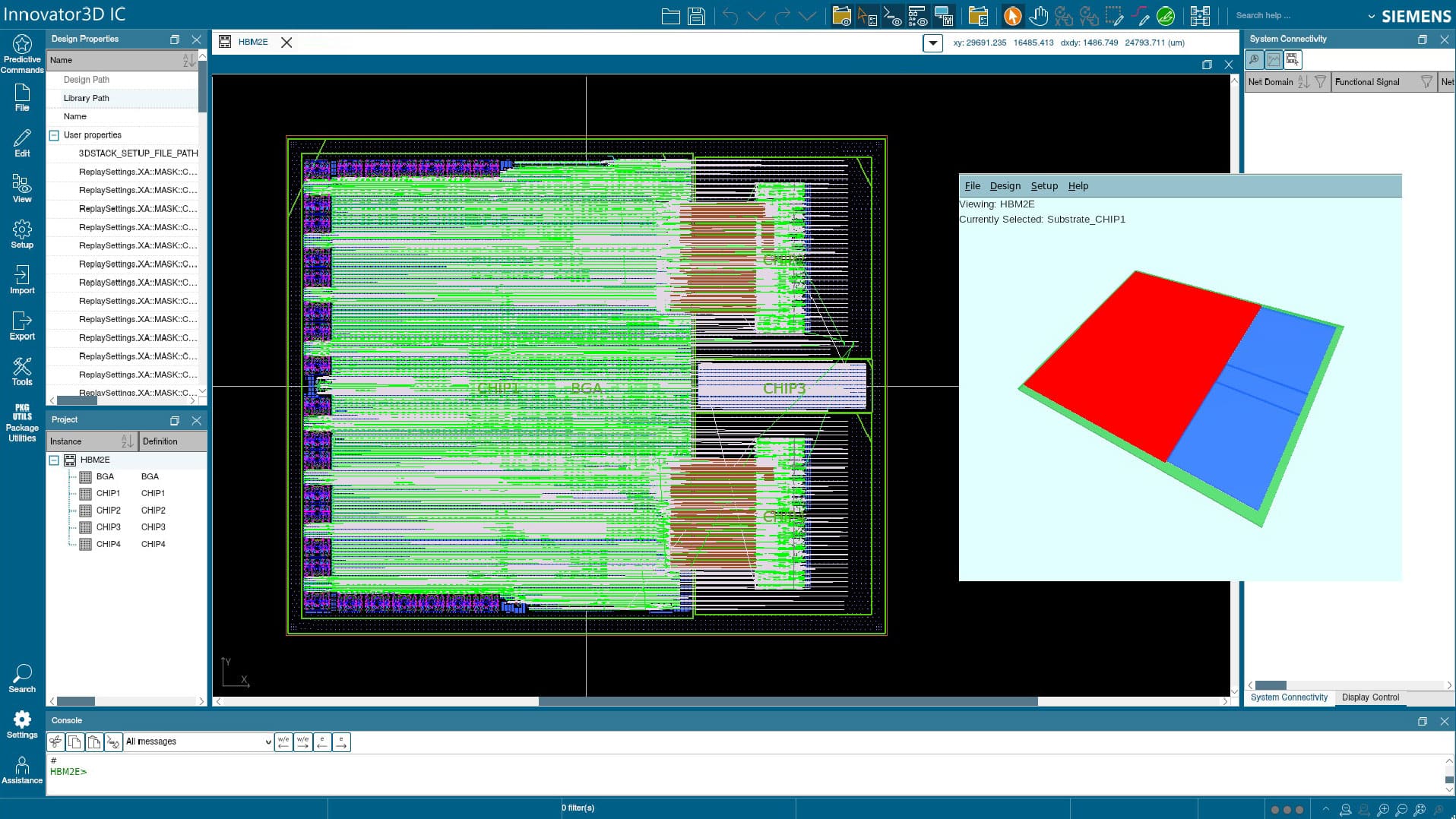

從3D-IC的角度來看,西門子的Calibre 3DSTACK解決方案對於台積電最新的3Dblox標準進行了認證。這項認證延續了雙方在台積電3DFabric先進封裝技術的熱分析要求方面的長期合作。

此外,兩家公司還合力釋放西門子Tessent軟體在3D-IC可測試性設計(DFT)實作方面的潛力,使台積電生態系統客戶和先進節點的合作夥伴能夠在此受益。台積電和西門子合作使用3Dblox標準來克服2nm及更小幾何形狀的特殊IC測試與診斷挑戰,攜手開發新的3D-DFT方法,包括良品晶片(KGD)迴路測試和實體感知晶粒間故障測試與診斷。

台積電設計基礎架構管理部門負責人Dan Kochpatcharin表示,西門子是台積電的長期策略合作夥伴,透過提供更多能支援台積電最新技術的優質解決方案,持續為台積電的Open Innovation Platform(OIP)生態系統提供助益。