西門子數位化工業軟體近日在台積電2021開放創新平台(OIP)生態系統論壇中宣布系列與台積電合作帶來一系列的新產品認證,雙方在雲端支援IC設計以及台積電的全系列3D矽晶堆疊及先進封裝技術3D Fabric方面,已經達成關鍵的里程碑。

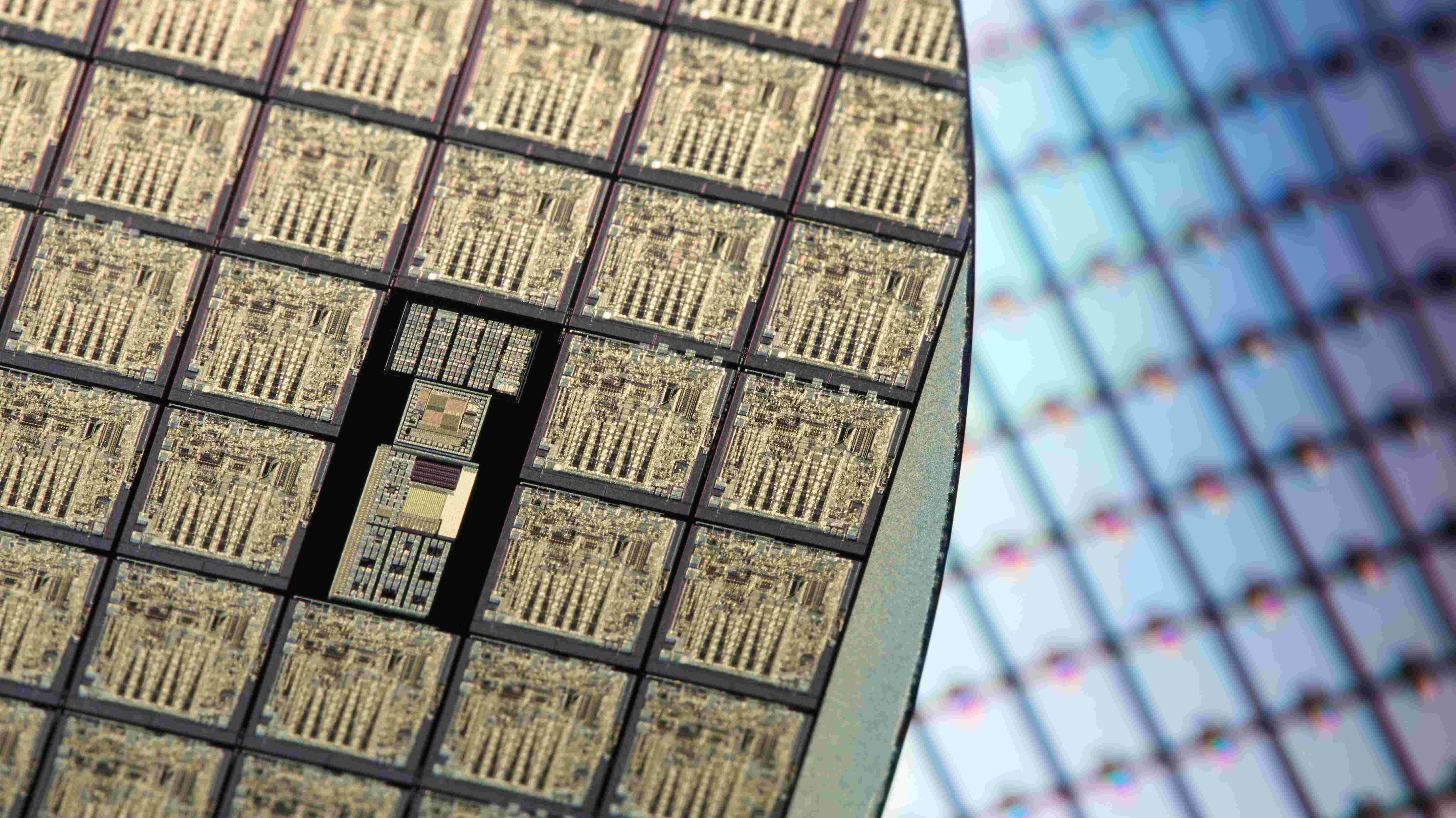

西門子有多項EDA產品最近通過了台積電的N3與N4製程認證,包括Calibre nm Platform西門子領先的IC Sign-off實體驗證解決方案;以及Analog Fast SPICE平台可針對奈米級類比、無線射頻(RF)、混合式訊號、記憶體與客製化數位電路,提供最先進的電路驗證功能。

西門子數位化工業軟體ICEDA執行副總裁Joe Sawicki表示,台積電持續開發創新的矽製程,支援雙方共同客戶創造全球最先進的IC產品。西門子很榮幸能與台積電長期合作,持續提供推動改變的技術,支援我們共同客戶更快將創新IC推進市場。

西門子對台積電最新製程的支援承諾更延伸至台積電3D Fabric技術。目前,西門子已成功滿足台積電3DFabric設計流程的設計要求。在鑒定流程中,西門子改進了其xPD工具,以支援使用自動化避免與矯正功能處理整合式扇出型晶圓級封裝(InFO)設計規則。此外,Calibre 3D STACK、DRC和LVS也獲得了台積電最新的3Dfabric科技(包括InFO、CoWoS和TSMC-SoIC)的支持與認證。對客戶而言,這些支援3D Fabric的解決方案可助其縮短設計與Signoff週期,並減少手動介入相關的錯誤。

同時,西門子也與台積電合作,針對台積電的3D矽晶堆疊架構開發「可測試性設計」(DFT)流程。西門子的Tessent軟體可提供採用階層架構式DFT、SSN、改善的TAP與IEEE 1687 IJTAG網路技術的先進DFT解決方案,這些技術都符合IEEE 1838標準。Tessent解決方案具備擴充性、靈活性與易用性,可協助客戶佳化IC測試技術相關的資源。