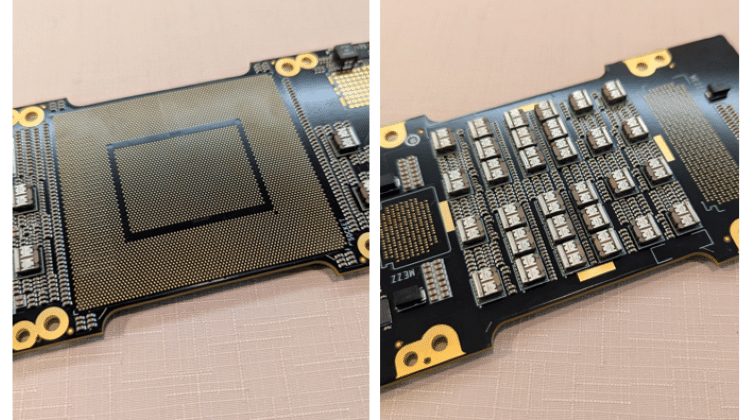

賽靈思(Xilinx)已開始投片20奈米可編程邏輯元件(PLD)和20奈米All Programmable元件。同時,賽靈思亦著手建置特定應用積體電路(ASIC)等級可編程架構–UltraScale。

賽靈思公司可編程產品事業群資深副總裁Victor Peng表示,賽靈思擬定了一個20奈米元件投片計畫,在高階元件方面,大幅領先最近競手對手1年以上;而在中階元件方面,則領先對手至少半年。再加上台積電的製程技術和賽靈思的UltraScale架構,運用Vivado設計套件進行協同最佳化,相信賽靈思將超前一年將系統級效能與整合度提升1.5至2倍,這等同於領先對手一個世代。

賽靈思持續與台積電合作,並採取與過去研發28HPL製程一致做法,將高階FPGA的需求導入台積電的20奈米研發流程。在28奈米的合作上,兩家公司共同打造出28奈米元件,並推出All Programmable FPGA、SoC及3D IC元件,讓賽靈思不論在價格/效能/功耗、可編程系統整合和降低物料清單(BOM)成本方面均領先對手一個世代。賽靈思現在將這個奠定其業界領先地位的28奈米成功經驗延伸到20奈米元件,再次率先將採用業界首款ASIC等級可編程架構UltraScale設計的元件進入投片階段。

賽靈思網址:www.xilinx.com