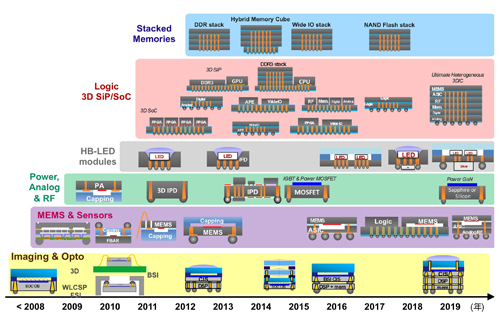

聯電矽穿孔(TSV)製程將於2013年出爐。為爭食2.5D/三維晶片(3D IC)商機大餅,聯電加緊研發邏輯與記憶體晶片立體堆疊技術,將採Via-Middle方式,在晶圓完成後旋即穿孔,再交由封測廠依Wide I/O、混合記憶體立方體(HMC)等標準組裝晶片。目前規畫於今年第四季邁入產品實測階段,並於2013年展開商用量產。

|

| 聯華電子市場行銷處長黃克勤認為,3D IC邁向普及仍需2~3年時間,原因包括製造成本過高、EDA工具仍未完備等。 |

聯華電子市場行銷處長黃克勤表示,聯電與記憶體大廠爾必達(Elpida)正聯手打造28奈米(nm)晶圓TSV製程,加速2.5D和3D IC問世。現基於Via-Middle的TSV生產技術已到位,今年第三季將在中段製程(MEOL)試作邏輯晶片與記憶體堆疊,並於第四季結合台灣半導體封測廠技術能量,展開產品層級封裝(Product Level Packaging)與晶片效能、可靠度測試。

在半導體摩爾定律(Moore’s Law)演進遭遇瓶頸之際,2.5D及3D IC設計將大幅增強晶片效能、頻寬支援,同時能縮減功耗與印刷電路板(PCB)占位空間。因此,黃克勤強調,聯電不斷加碼投資研發,並拉攏半導體設備、封測及晶片業者,按部就班建立3D IC生態系統,除能延續摩爾定律外,亦能擴張旗下晶圓代工業務範疇。預計明年聯電的TSV製程導入商用後,營收也將顯著加溫。

與此同時,考量TSV未來將應用在20奈米以下先進製程,勢將面臨裸晶體積縮小後,微縮TSV直徑與提升對位精準度的技術挑戰,聯電亦搶先展開新技術布局。黃克勤透露,聯電將跳脫傳統TSV製作方式,改良TSV製程結構,藉以優化3D IC的可靠度與功能表現。

無獨有偶,台積電亦致力發展2.5D/3D IC一條龍製程–CoWoS(Chip on Wafer on Substrate),並預計於2013年開始放量,衝刺3D IC晶圓代工的市占版圖。不過,該方案幾乎囊括TSV、晶片堆疊與部分封測製程,可能發生與封測廠相互爭利的情況,引發業界關注;相較之下,聯電仍謹守晶圓代工分際。

黃克勤指出,聯電的2.5D/3D IC解決方案,僅鎖定Via-Middle的TSV服務,針對晶片商的設計精準鑿穿晶圓,而矽穿孔露出(Via-reveal)或晶片堆疊組裝等後段製程(BEOL)再交由封測業者操刀。由於專注TSV供應,將能避免設備投資負擔過重或引來激烈的市場競爭,同時也能擴展客源與封測廠合作夥伴,削減物料清單(BOM)成本,促進3D IC價格更快達到市場甜蜜點,加速普及。

據了解,Via-Middle模式係晶圓產出後才增添一道TSV工序,與直接在晶圓製造時就進行TSV的Via-First,或晶圓交至封測廠手中才導入TSV的Via-Last兩種方案相比,包括晶圓品質、良率及晶片商對設計的掌握度均較為出色,可望隨著3D IC生態系統茁壯而嶄露鋒芒,成為晶圓代工廠的金雞母。