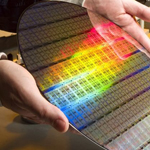

IC設計公司與晶圓代工廠的合作將邁向類IDM模式。進入20奈米製程世代,將牽動半導體設備、電子設計自動化(EDA)工具、IC電路布局與封測作業全面革新,導致產業鏈須投資大量資源;因此,晶圓代工廠與晶片商為避免個別財務負擔過重,將更加緊密合作,並共同分攤研發設備與人力開支,加速推進20奈米以下製程問世。

|

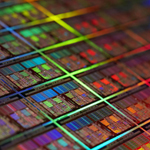

| 中國半導體行業協會IC設計分會理事長暨清華大學微電子學研究所長魏少軍提到,SoC邁向3D架構後,要發揮異質晶片堆疊效益,軟體應用層的重要性將更加突顯。 |

中國半導體行業協會IC設計分會理事長暨清華大學微電子學研究所長魏少軍表示,20奈米以下製程為半導體生態系統帶來根本性的改變,由單家晶圓代工廠或整合元件製造商(IDM)推動,都將面臨研發資金匱乏、技術瓶頸等問題;因此,現階段台積電、格羅方德(GLOBALFOUNDRIES)與聯電等晶圓大廠,以及高通(Qualcomm)、博通(Broadcom)等重量級晶片商,均意識到集結眾人之力才是發展20、16或14奈米製程的王道,開始擴大供應鏈垂直合作計畫。

魏少軍分析,市場一般認為每世代製程演進可大幅提升晶片效能並降低成本;然而,20奈米以下製程技術複雜,需要新的曝光設備及EDA工具,預料僅有少數幾家業者有足夠本錢投資,在產能有限的情況下,成本下降幅度將大不如前。以英特爾(Intel)為例,從45到32奈米可降低10.1%成本,但由32推進至22奈米卻僅縮減3.3%成本,推估進入16奈米降價空間將更加受限。

魏少軍也指出,多半IDM積極走向輕晶圓廠(Fablite)經營模式,緊縮半導體設備、廠房投資計畫,主要原因除市況低迷外,跨越28奈米後的先進製程研發費用龐大,且技術投資風險高得嚇人更是一大關鍵。預估未來少數晶圓代工廠與Fabless晶片商將成半導體資本支出主力,而晶圓廠也將慎選客戶,妥善利用產能並分散投資風險,創造新的類IDM合作模式。

格羅方德技術長辦公室先進技術架構主管Subramani Kengeri透露,目前格羅方德即以類IDM策略,推展旗下28奈米業務。透過與客戶一起投入早期晶片設計,將提供客製化服務並加速產品研發時程;未來在20奈米以下製程,該公司也將沿用此一發展策略,持續加強與IC設計公司合作,進一步提高生產效率與降低投資風險。

另一方面,隨著20奈米以下製程難度與投資劇增,業界亦已提出半導體產業將進入後摩爾定律(Post-Moore’s Law)時代的看法,認為晶片製程演進將趨緩,轉向2.5D/3D IC的系統單晶片(SoC)技術支線發展。魏少軍認為,先進製程卡關將加速平面互補式金屬氧化物半導體製程走向盡頭,推助鰭式電晶體(FinFET)與異質晶片堆疊技術崛起,包括晶圓代工、晶片商與封測廠均已全力展開部署。