第四代雙倍資料率(DDR4)記憶體時代即將到來。益華電腦(Cadence Design Systems)與台積電在DDR4矽智財(IP)方案合作有成,除搶先推出DDR4同步動態隨機存取記憶體(SDRAM)實體層(PHY)及記憶體控制器設計IP系列產品外,亦已在台積電28奈米(nm)製程上成功驗證,將有助帶動DDR4市場的發展。

|

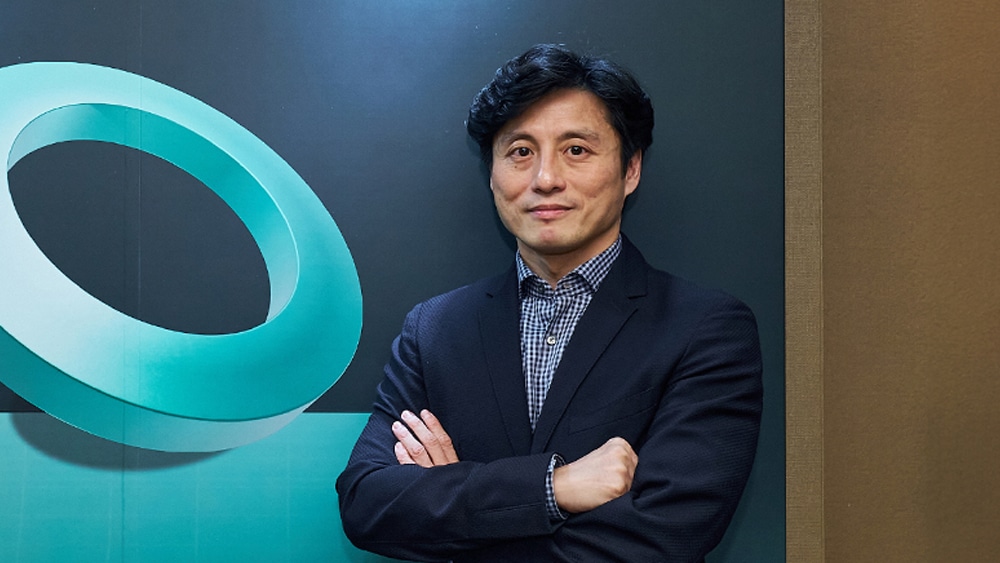

| 益華SoC實現事業群產品行銷總監Marc Greenberg表示,該公司可提供客製化DDR4設計IP方案,有助客戶創造產品差異。 |

益華SoC實現事業群產品行銷總監Marc Greenberg指出,該公司的IP產品組合,可針對廠商的特定需求提供客製化的解決方案,進而幫助客戶在市場上推出差異性產品,且縮短上市時程。

有鑑於個人電腦、行動裝置對DRAM存取速率和記憶體容量的需求日益升高,聯合電子裝置工程協會(JEDEC)預計於今年正式發布DDR4標準;瞄準下一代DDR商機,益華現已針對DDR4的標準草案,著手開發相關IP解決方案,並已能在台積電28奈米高效能(HP)和高效能行動運算(HPM)製程,實現該IP設計,可望搶先插旗DDR4市場。

據了解,與DDR3標準相較,個人電腦、行動裝置DRAM嵌入DDR4的解決方案,可增加50%存取速率及兩倍記憶體容量,並降低40%的位元轉換功耗,可望為DRAM帶來效能上的優勢。

值得一提的是,益華的DDR4 IP於實體層的傳輸速率,已超過DDR-2400標準草案的設定,將能滿足下一代運算、網路、雲端基礎建設和家庭娛樂設備的需求;此外,該DDR4 IP解決方案亦能與DDR3和DDR3L標準相容、互通無礙。

與此同時,台積電28HPM製程,能實現益華DDR4 IP低功耗、全數位化(All-Digital)行動實體層的設計,且其傳輸速度能勝過DDR3的DDR-1600和DDR-1866標準,以及LPDDR2標準的最大傳輸量,將有助於統單晶片(SoC)設計人員在下一代的行動裝置設計中,快速導入最新低功耗記憶體技術。