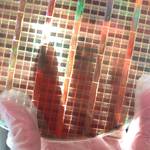

工研院於日前成立三維立體積體電路(3DIC)研發實驗室,樹立台灣晶片技術由平面走向立體堆疊與異質整合的里程碑。該實驗室在經濟部科專計畫的支援下,預計在4年間投入新台幣16億元的研發經費,並在先進堆疊系統與應用研發聯盟( Ad-STAC)協助下,以建立12吋3DIC的完整製程為目標,期待能率先推出3DIC的全方位解決方案。

|

| Ad-STAC榮譽會長胡定華表示,結合工研院3DIC實驗室與Ad-STAC的產業資源,將能進一步帶動台灣的半導體產業邁向下個10年的榮景。 |

Ad-STAC榮譽會長胡定華表示,Ad-STAC聯盟成員包含應用材料(Applied Materials)、SUSS MicroTec、聯電、漢民、矽品、日月光、Atotech、杜邦(DuPont)、力鼎、亞普(Air Products)、布魯爾科技(Brewer Science)、住程科技、弘塑、東京大學、DISCO、智勝、益華電腦(Cadence)、BASF、Tazmo等,將聯合產學資源,與工研院共同合作開發完備且整合的3DIC核心製程–矽穿孔(TSV)技術,延續台灣在半導體領域的優勢。

經濟部技術處處長吳明機強調,台灣的半導體產業位居世界第一,但近年來受到鄰近國家如韓國的嚴峻挑戰,不僅產業界關心台灣在下個階段的優勢為何,政府也積極思考。幾經考量之下,技術處決定投入3DIC的研發。相信此項研發案將能加強台灣在半導體產業的主導力量。

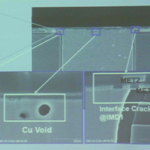

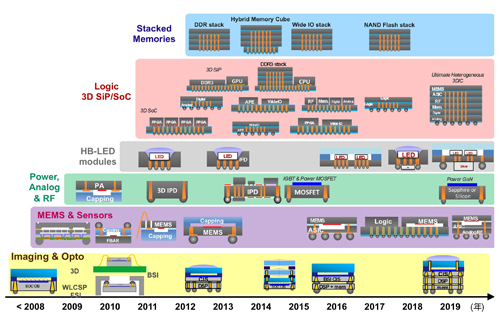

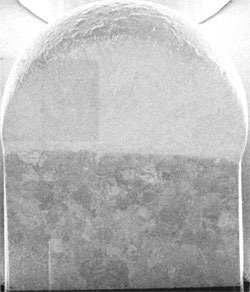

半導體製程依循摩爾定律(Moore’s Law)的發展下,不斷朝微縮方向前進,但目前也已遭遇發展瓶頸,在無法繼續在二維平面上持續縮小半導體製程的壓力下,朝向立體製程方向的3DIC便成為此時的出路。工研院電光所副所長高明哲指出,目前實驗室的研發階段已成功達成二十層堆疊層的目標,但該測試IC也僅符合最低的電氣測試,尚無法確認各IC在堆疊後的功能有效發揮。為能有效提升IC的良率,工研院電光所將投入四十位研究人員,再加上資通所八十位同仁共組成研發團隊,共同來解決TSV技術的瓶頸。

高明哲透露,TSV技術較過往慣用的打線接合(Wire Bonding)技術昂貴,初期將鎖定高輸入/輸出(I/O)及高頻應用的應用,待未來技術發展成熟後,才會延伸應用廣度,提升各階應用的效能。屆時,因各元件的效能都符合高效的標準下,將可大幅提升系統的整體效能。