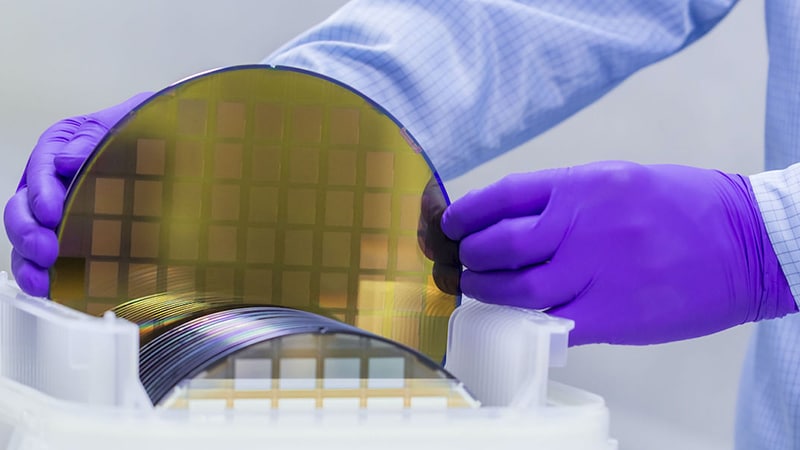

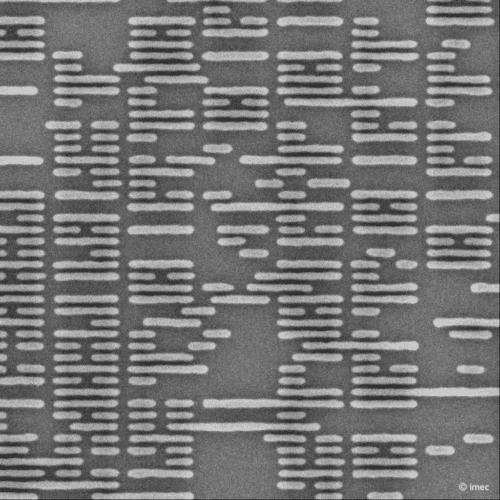

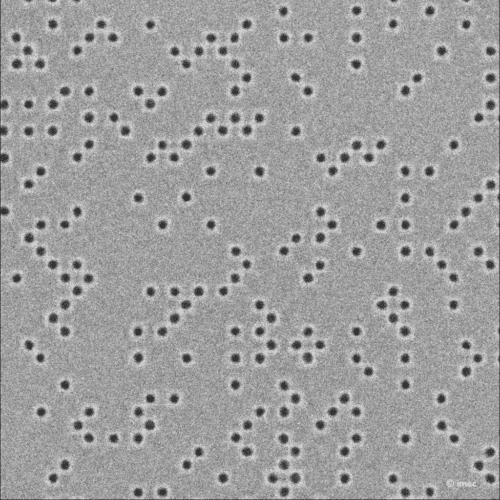

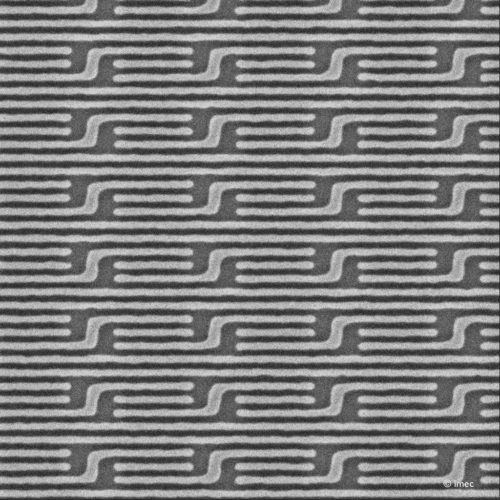

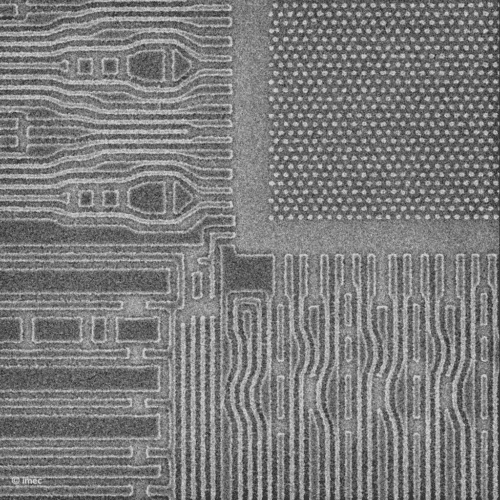

比利時微電子研究中心(imec)在荷蘭費爾德霍溫與艾司摩爾(ASML)合作建立的高數值孔徑(High-NA)極紫外光(EUV)微影實驗室中,利用數值孔徑0.55的極紫外光曝光機,發表了曝光後的圖形化元件結構。在單次曝光後,9奈米和5奈米(間距19奈米)的隨機邏輯結構、中心間距為30奈米的隨機通孔、間距為22奈米的二維特徵,以及間距為32奈米的動態隨機存取記憶體(DRAM)專用布局全部成功成形(圖1~圖4),採用的是由imec與其先進圖形化研究計畫夥伴所優化的材料和基線製程。透過這些研究成果,imec證實該微影技術的生態系統已經準備就緒,能夠實現高解析度的High-NA EUV單次曝光。

由艾司摩爾與imec共同成立於荷蘭費爾德霍溫的High-NA EUV微影實驗室在近期啟用後,客戶現在可以使用TWINSCAN EXE:5000高數值孔徑極紫外光曝光機來開發非公開的High-NA EUV應用案例,這些案例也能運用客戶各自的設計規則和佈局。

imec成功利用單次曝光,形成間隔為9奈米與半線寬為5奈米的隨機邏輯結構,相當於間距為19奈米,圖形頂端(Tip-to-tip)的間距達到20奈米以下。中心間距為30奈米的隨機通孔充分展示了絕佳的圖形保真度與關鍵尺寸均勻度。此外,間距為22奈米的二維特徵也展現了傑出的性能,突顯了利用高數值孔徑微影技術來實現2D佈線的發展潛力。

除了邏輯結構,imec也成功利用單次曝光,為動態隨機存取記憶體(DRAM)製出把電荷儲存節點連接墊(Storage Node Landing Pad)與周邊位元線相互整合的元件圖形。這項成就彰顯了高數值孔徑技術的潛能,可望透過單次曝光來取代多層光罩的曝光需求。

取得這些突破性成果後,imec攜手艾司摩爾與其夥伴,開始緊鑼密鼓地進行準備工作,為第一代High-NA EUV微影技術來籌備圖形化生態系統與量測技術。在進行多次曝光之前,imec準備了專用的晶圓堆疊(包含先進光阻、塗布底層及光罩),並把像是光學臨近校正(OPC)、整合圖形化及蝕刻技術等High-NA EUV基線製程整合到0.55NA EUV曝光機台上。

imec運算技術及系統/運算系統微縮研究計畫的資深副總裁Steven Scheer表示,很高興能在艾司摩爾與imec共同建立的實驗室展示全球首次利用High-NA技術完成的邏輯及記憶體元件圖形化,這也是業界應用的首次認證。結果顯示,在利用單次曝光成像來積極微縮2D特徵圖形的方面,High-NA EUV技術展現了獨特的潛能,不僅改善了設計彈性,也減少了圖形化的成本與複雜度。面向未來,我們期待能夠提供價值洞見給圖形化生態系統的合作夥伴,協助他們進一步推動High-NA EUV專用材料及設備的發展。

imec執行長Luc Van den hov則指出,此次成果證實了高數值孔徑EUV技術具備長遠預測的解析度能力,目標是利用單次曝光來製出間距為20奈米以下的金屬層。因此,High-NA EUV技術將會為延續邏輯和記憶體技術的尺寸微縮提供莫大的助益,這也是推進元件發展藍圖邁向埃米世代的一大重要支柱。這些早期技術展示全都是因為艾司摩爾與imec共同實驗室的成立才得以實現,該實驗室能讓我們的合作夥伴加速把高數值孔徑微影技術引進量產。