人工智慧AI發展全面展開,可編程邏輯廠商美商賽靈思(Xilinx)認為,未來已經沒有一個架構可以滿足所有的應用需求,因此該公司正式踏上轉型之路,舉辦賽靈思開發者大會(XDF),並發表未來幾年的技術與產品重點,全面擁抱人工智慧的發展趨勢,以資料中心(Data Center)為發展策略的起點,目標為打造靈活應變、萬物智慧的世界。

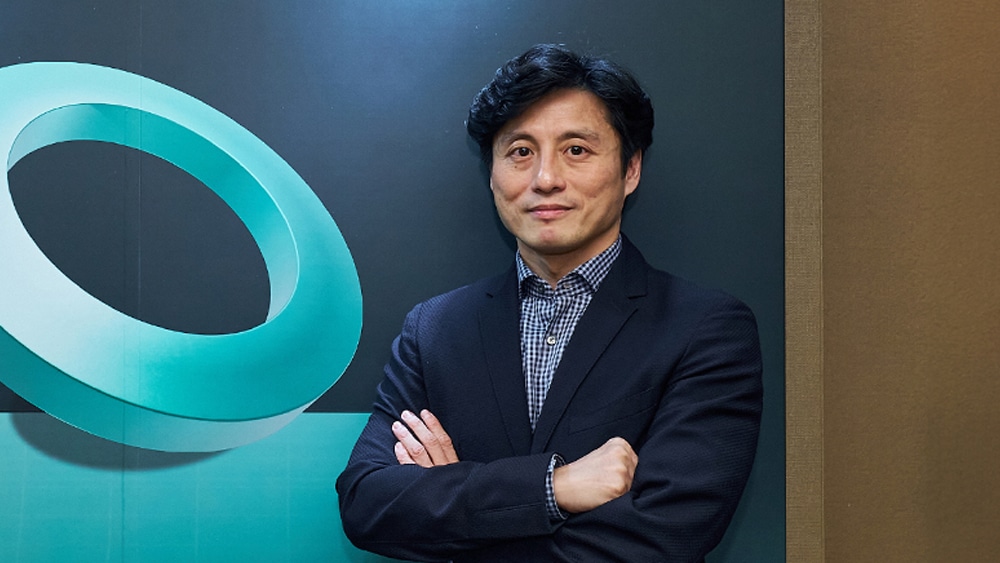

一直以可編程技術為發展重點的Xilinx,2018年3月正式啟動策略轉型工作,宣示該公司從元件廠商轉型為平台廠商,提出自行調適運算加速平台(Adaptive Compute Acceleration Platform, ACAP)發展核心,旋即於10月推出第一款產品Versal。Xilinx總裁暨執行長Victor Peng表示,Versal字面上是由Variety與Universal組合而成,希望在技術與應用上可以兼顧多樣性與通用性。

在AI無所不在的時代,AI應用日新月異,晶片設計週期已經落後創新的速度,因此Peng認為,FPGA彈性的特點可以應用在AI的創新上,一般新晶片設計週期高達24個月,透過ACAP平台的協助,可將AI模型加以拆解,變成數個不同的發展(Develop)、優化(Optimize)、部署(Deploy)流程,該平台動態範圍廣泛彈性,可針對不同的應用調整需要的加速範圍。

Versal ACAP結合純量處理引擎(Scalar Processing Engine)、Arm Cortex-A72與Arm Cortex-R5,以及自行調適硬體引擎(Adaptable Hardware Engine),可動態重新配置,即時加速能力最高達八倍;DSP引擎可提供高準確性浮點運算與低延遲;AI引擎具有高傳輸率、低延遲與高效率,可協助AI推論與高階訊號處理,搭配先進記憶體和介面技術,可提供強大的異質加速能力。不管是軟體開發者、資料科學家或是硬體開發者,只須利用符合業界標準設計流程的工具、軟體、函式庫、IP、中介軟體以及框架,就能針對其硬體與軟體進行編程與最佳化。據了解,Versal採用台積電7奈米FinFET製程,正式量產時間為2019年第二季。

Xilinx也以現有UltraScale+ FPGA為基礎,發表Alveo U200與Alveo U250加速卡,就機器學習而言,Alveo U250的即時推論傳輸率比高階CPU高出20倍,甚至在低於2毫秒的低延遲應用方面,也比高階GPU這類固定功能加速器高出4倍。此外,Alveo加速器卡的延遲較GPU減少3倍,在資料庫搜尋等應用方面大幅加速、並提供較CPU高出90倍的效能。