英特爾(Intel)推出嵌入式多裸晶橋接(Embedded Multi-Die Interconnect Bridge, EMIB)技術,並提供原本用於內部自有產品的高密度模組測試(High Density Modular Test, HDMT),以降低14奈米(nm)晶圓代工客戶的封裝與測試成本,同時加速產品上市時程。

英特爾封裝測試技術發展副總裁兼董事Babak Sabi表示,EMIB提供晶圓代工客戶一種全新的封裝選擇;相對於以往昂貴的矽中介層(Silicon Interposer)與矽穿孔(Through Silicon Via, TSV)等裸晶互連技術,採用EMIB方案將可幫助客戶降低成本與封裝的複雜度。

據了解,EMIB為具備低成本與簡單特性的2.5D封裝設計,可用於14奈米製程,代替易增加成本與設計複雜度的TSV與特殊矽中介層技術。該技術僅需於封裝內裸晶相連的部分內嵌一顆小型矽橋接晶片,便可在單一封裝中實現高密度的裸晶對裸晶(Die-to-Die)連接。另外,標準覆晶(Flip Chip)封裝係用以傳送較大的功率,並將高速訊號直接由晶片傳送到封裝基板。英特爾將於2015年開始提供EMIB技術給晶圓代工客戶進行樣品生產。

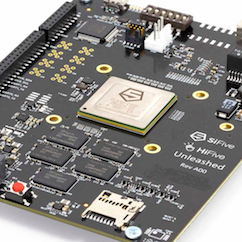

與此同時,英特爾也同步開放以往僅用於自家產品測試的HDMT平台。該平台結合硬體與軟體模組,適用於多種領域的產品測試,包括伺服器、系統單晶片(SoC)、物聯網(IoT)等,即日起已可開始提供客戶使用。

Sabi強調,英特爾的HDMT平台可加速測試程序與單位層級(unit-level)製程控制;由於從小量產品除錯到大量生產皆使用共同平台,因而能有效幫助客戶縮短上市時程並改善生產力,與傳統測試方案相比可明顯降低成本。