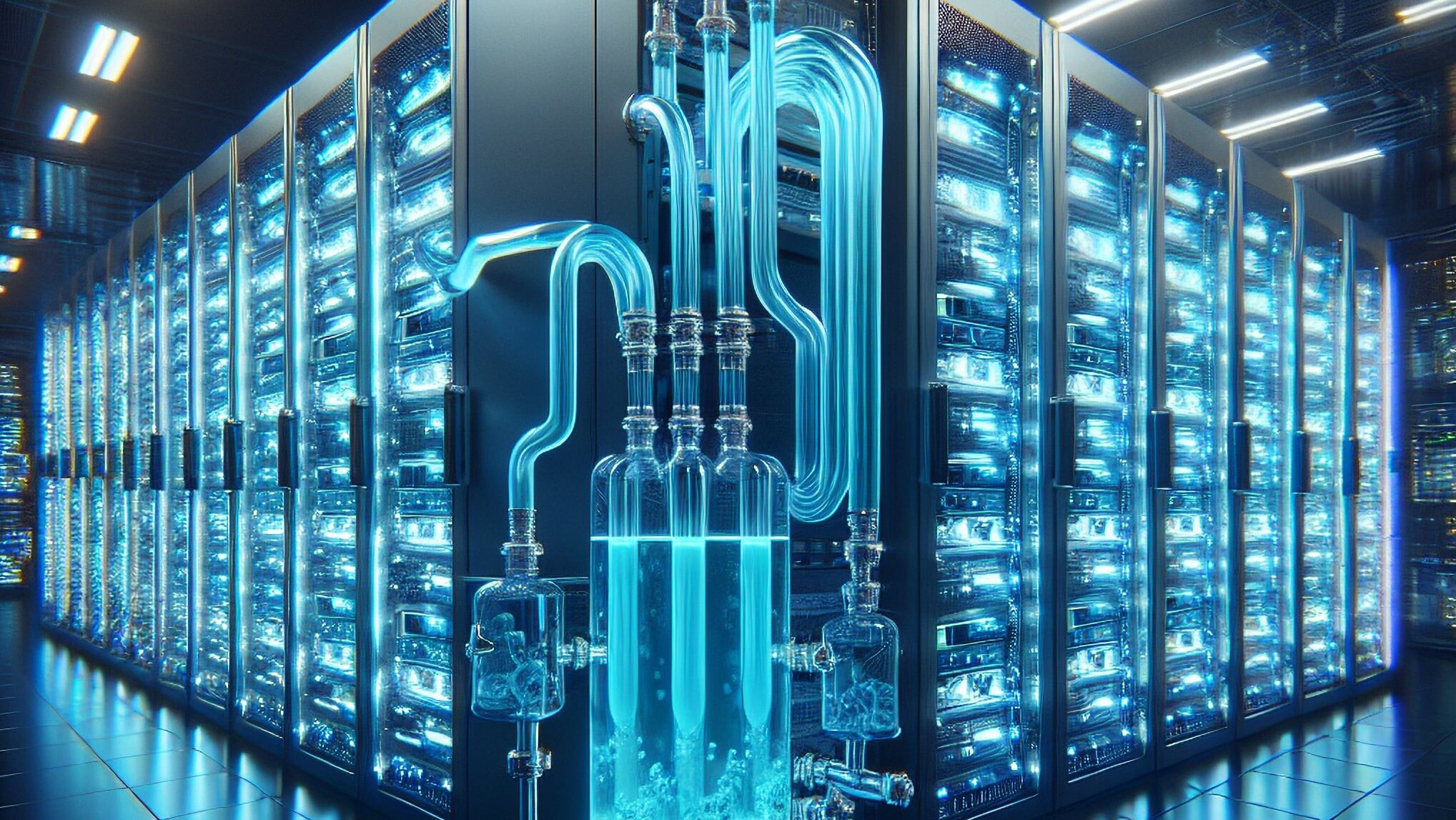

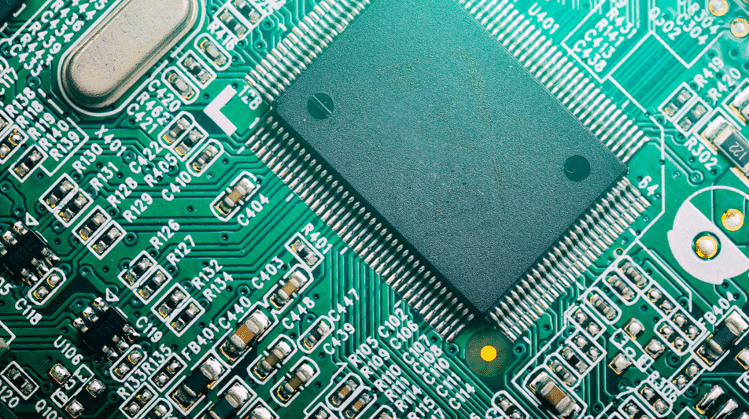

宜特宣布與國際客戶策略合作工程技術發展,成功研究出抵抗環境因素,克服高端產品(例如4G/長程演進計畫(LTE)、雲端伺服器)中之印刷電路板(PCB)爬行腐蝕(Creep Corrosion)的濕硫磺蒸氣試驗(Flower of Sulfur Test, FOS)驗證技術。這是繼2012年宜特研發出混流氣體試驗(Mixing Flower Gas Test, MFG)後,另一更有效且便宜之驗證爬行腐蝕現象的測試方法。

FOS試驗主要是測試PCB板上之金屬電路抗腐蝕的能力,依照ISA-71.04標準規範(環境氣體組成限制標準)與美國冷凍空調學會(ASHRAE)的規範,針對銀箔腐蝕反應速率必須小於20奈米(nm)/月;銅箔為30奈米/月。欲了解是否PCB板上的金屬電路達到此規範要求,在進行後續FOS試驗時,亦須先對金屬做前處理。宜特利用「化學蝕刻」與「機械拋光前處理」兩種前處理方式來試驗,發現「化學蝕刻」能更準確的了解到腐蝕反應速率。

宜特與IBM、戴爾(Dell)及聯想等企業,開發出濕硫磺蒸氣試驗(FOS)的爬行腐蝕驗證測試,與MFG相比,此技術可以用較低成本、較快速度驗證出PCB的抗爬行腐蝕能力。

宜特網址:www.istgroup.com

頒發「ESCO-經營績優獎(非中小企業組)」予台灣西門子,由智慧建築業務總監彭樹裕代表受獎。-e1766140089707.jpg)