生成式AI的興起,不僅讓半導體產業將目光轉向先進封裝,同時也給晶片供應商有更充分的理由,採用更昂貴的先進製程來生產處理器晶片。然而,成本始終是一個必須解決的問題。因此,晶片微影技術領導廠商艾司摩爾(ASML)特別於SEMICON Taiwan期間,與業界分享其新一代高數值孔徑極紫外光(High NA EUV)微影技術的發展狀況,並特別強調該公司將協助晶片製造商簡化製造程序、提高產能,並降低晶圓生產時的耗電量。

導入High NA EUV可帶來多重效益

艾司摩爾High NA EUV產品管理副總裁Greet Storms表示,為持續推動電路微縮,讓摩爾定律向前邁進,艾司摩爾不只要推出解析度更好的微影設備,同時也深知這些技術創新必須能為半導體製造商帶來更多實質效益,例如良率改善、產能增加與持有/操作成本下降等,才能提高客戶採用新一代設備的意願。

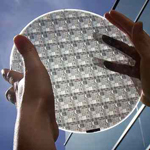

在解析度提升方面,艾司摩爾最新一代High NA EUV微影技術透過導入新的光學元件,將數值孔徑(Numerical Aperture, NA)從0.33提升至0.55,以支援更高的成像解析度。High NA EUV的臨界尺寸(Critical Dimension, CD)可達到8nm,讓晶片製造商可以在同樣單位面積的晶片上實現較現今高出2.9倍的電晶體密度;且成像對比度較0.33 NA EUV提高40%,可大幅降低成像缺陷。

不僅缺陷更少,導入High NA EUV之後,量產邏輯和記憶體晶片的製程步驟也可以減少,進而降低成本、縮短生產週期。同時,High NA EUV與現有的EUV設備,內部有不少設計是通用的,因此能降低客戶轉換設備時的導入風險跟研發成本。High NA EUV微影系統已於2023年底開始陸續出貨,產能預計每小時可曝光超過185片晶圓,將支援2奈米以下邏輯晶片及具有相似電晶體密度的記憶體晶片量產。

降低耗電量是重點改良方向

除了提升曝光性能外,Storms特別強調,降低製程耗電量也是艾司摩爾正在追求的目標。這個議題可以分成兩個層面來看,首先,由於在先進製程中導入EUV技術可簡化製程步驟、減少光罩數量,達到產能和良率提升,因此生產每片晶圓的用電量其實是降低的。艾司摩爾估計,若在先進製程中導入EUV和High NA EUV微影系統,到2029年,使用ASML微影技術生產每一片晶圓使用的100度電,將為整體製程帶來節省200度電的效益。

然而,EUV機台本身的耗電量確實相當可觀,因此,除了降低全製程的耗電量外,降低曝光設備的耗電量,也是艾司摩爾努力的方向。過去5年,EUV設備曝光一片晶圓的用電量,已降低40%。艾司摩爾的目標是,到2025年前,EUV跟High NA EUV設備的耗電量,要再降低30%~35%。