IAR Systems與CAES容錯處理器設計中心之Gaisler宣布新合作關係。IAR Systems近期將釋出新版IAR Embedded Workbench for RISC-V,新版本將支援Gaisler所推出之NOEL-V太空級RISC-V處理器。

NOEL-V為採用RISC-V架構打造之可合成VHDL處理器,具備可高度配置並提供多元組態設定,涵蓋範圍從支援Linux的高效能架構到空間最佳化的微控制器解決方案。NOEL-V亦設計為可納入容錯功能,在充斥天然幅射的太空環境中能自動校正各種失效,使元件能持續執行程式而不中斷。

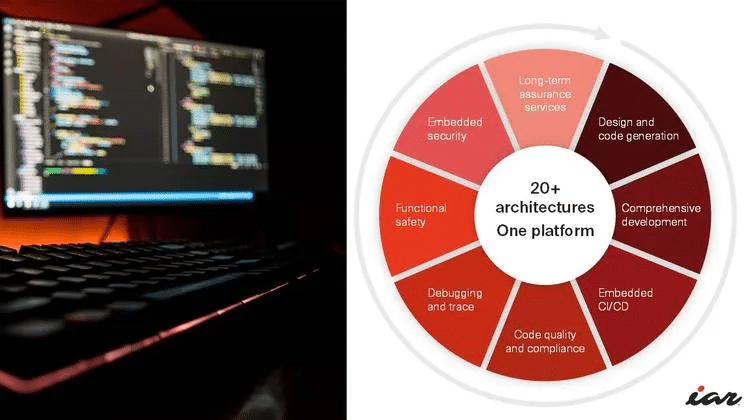

IAR Embedded Workbench for RISC-V為一完整的開發工具鏈,透過簡單易用的整合開發環境為開發人員提供所有需要的資源。工具鏈包含完備的除錯功能,並包括各種多核心除錯與分析功能,如複雜程式碼與資料斷點、執行階段堆疊分析、呼叫堆疊可視化,以及程式碼覆蓋範圍分析。

IAR I-jet除錯器提供能對接NOEL-V系統的高效率除錯介面,其採用標準RISC-V JTAG除錯介面規格,並將包含於預計2023年12月釋出之新版可免費下載的NOEL-V FPGA範例位元流(Bitstream)中。

開發基於NOEL-V處理器的關鍵任務應用開發人員,將可透過IAR Compiler的編譯器優化技術來到更高性能,並運用IAR完備除錯器之優勢。

總體而言,此合作關係將為NOEL-V用戶提供使用另一個完整開發工具鏈的彈性,進而擴展Gaisler已提供的廣泛工具集。

對於IAR Systems而言,此次合作是進入太空市場的重要進程,因為NOEL-V架構在此市場占有領導地位。